# **MPC860 Interface with Generic MC68000 Bus**

The main point of this document is to demonstrate an interface between an MPC860 and a generic MC68000 peripheral. It should be noted that this interface only supports read or write accesses initiated by the MPC860 to the peripheral. For the purpose of this document the following parameters are assumed:

- Interface is between an MPC860 and a lower speed MC68000 peripheral.

- MC68000 peripheral is a 16 bit port size that is defined as part of the upper data bus.

- The MC68000 peripheral is not a bus master.

- The MPC860 user programmable machine (UPM) is programmed to generate the proper timing of the signals.

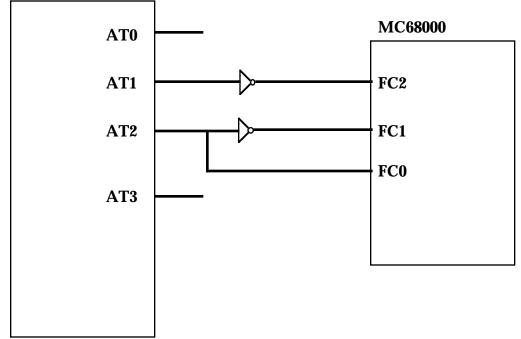

- General purpose input/output pins available from the MPC860 are used to accommodate function code programming of the MC68000. Alternatively, external logic could be used to make the existing signals behave like MC68000 function code signals.

# Programming the Option, Mode and Base Registers

The option and base registers of the MPC860 must be programmed as follows for this type of interface. The option and base registers must be programmed for a 16 bit (no-parity) non-bursting port. The following tables have been appended from section 15 of the MPC860 Manual.

| Bits  | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                    | Function                        |

|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 20-21 | PS(0:1)  | <b>Port Size.</b><br>This field specifies the port size of the memory region.                                                                                                                                                                                                                                                                  | 10 = 16 bit port size           |

| 22    | PARE     | Parity Enable.<br>This bit is used to enable of the<br>parity charity checking on this<br>bank.                                                                                                                                                                                                                                                | 0 = disable parity              |

| 24-25 | MS(0:1)  | Machine Select.<br>This field specifies the machine<br>selected for the memory<br>operations handling.                                                                                                                                                                                                                                         | 10 = U.P.M.A or<br>11 = U.P.M.B |

| 31    | V        | Valid Bit.<br>This bit indicates that the contents<br>of the base register and option<br>register pair are valid. The CS<br>signal does not assert until the V<br>bit is set.<br>Note: An access to a region that<br>does not have the V bit set may<br>cause a bus monitor time out.<br>Following a system reset, the V bit<br>is set in BR0. |                                 |

#### Table 15-14. Base Register

| Bits | Mnemonic | Description                                                                                                                                                                                                                                                                          | Function                                                                                                     |

|------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| 20   | SAM      | Start Address Multiplex.<br>This attribute determines how the<br>address is output on the first cycle<br>of an external memory access<br>read or write when the memory<br>access is handled by UPMA or<br>UPMB.                                                                      | 0 = Address pins are the<br>address requested by<br>the internal master.<br>Disable address<br>multiplexing. |

| 23   | BI       | Burst Inhibit.<br>This attribute decides whether or<br>not this memory bank supports<br>burst accesses. In a non-burst<br>case, the memory controller drives<br>the BI signal active when<br>accessing this memory region.<br>Following a system reset, the BI<br>bit is set in OR0. | 1= Drive BI asserted. The<br>bank does not<br>support burst<br>accesses.                                     |

#### Table 15-15. Option Register

| Bits | Mnemonic  | Description                                                                                                                                                                                                                                                              | Function                                                                                                                                                                          |

|------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8    | ΡΤΑΕ      | <b>Periodic Timer A Enable.</b><br>This bit allows the periodic timer A to request service. Note: Following a system reset, the PTAE bit is reset.                                                                                                                       | 0 = Periodic timer A is<br>disabled                                                                                                                                               |

| 19   | GPL_A4DIS | <b>GPL_A4 Output Line</b><br><b>Disable. This</b> bit determines if the<br>UPWAITA*/ GPL_A4* pin will<br>behave as an output line<br>controlled by the corresponding<br>bits in the UPMA array (GPL4A*).<br>Note: Following a system reset,<br>the GPL_A4DIS bit is set. | 1 = UPWAITA/GPL_A4<br>behaves as a<br>UPWAITA when:<br>The G4T4/DLT3 bit in<br>the UPMA is<br>interpreted as DLT3.<br>The G4T3/WAEN bit<br>in the UPMA is<br>interpreted as WAEN. |

### **Programming the Signals for a Successful MPC860 and MC6800 Generic Bus Interface:**

For this interface the MPC860 signals are programmed to communicate with the MC68000 Bus. With examination of the timing specifications, the MPC860 can be programmed to interface with any of the MC68000 peripherals. In each case the UPM can be programmed to accommodate different part speeds.

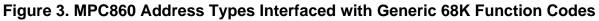

The active low MPC860 chip select signal is programmed to the MC68000 address strobe. The chip select's assertion can be interpreted as a MC68000 address strobe to emulate the MC68000 bus operation. Because you can directly manipulate chip select timing via the UPM, you can reproduce the timing of the MC68000 AS\* signal.

The active low signals BS[0] and BS[1] can be programmed for the upper and lower data strobe signals of the MC68000. BS[0] and BS[1] correspond with the byte lanes of the upper half of the data bus. The timing of these BS\* signals can also be directly manipulated via the UPM, enabling emulation of the MC68000 UDS\* and LDS\* signals.

The Read/Write signal of the MPC860 can directly communicate with the same signal on the MC68000. The timing is not a problem since the read/write signal is asserted directly after the transfer start signal.

When programming the function codes of the MC68000 bus, strict attention must be paid to the function code outputs. For the following explanation please refer to page 13-35 of the *MPC860 User's Manual* and page 3-9 of the *MC68000 User's Manual*. For the purpose of this example, UPM general purpose IN/OUTPUT lines are used to perform as function code signals. Timing of these signals is not critical, they merely must stay constant throughout the access to the MC68000 peripheral. However, only one function code may be programmed. It is also possible to generate the function codes in the hardware. Please see Figure 1-1 through Figure 1-3 for a detailed diagram of the interface and the function code hardware. Note that this configuration does not support the MC68000 IACK signals. This only supports the following four function codes: supervisor program, supervisor data, user program and user data.

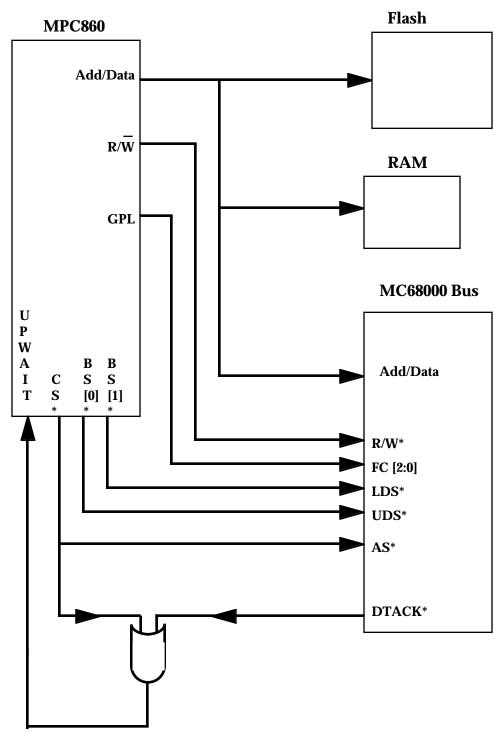

The DTACK\* signal must be handled by an external OR gate. This will generate an UPWAIT signal until the AS\* and DTACK\* signals are asserted. The UPM output signals will freeze as long as UPWAIT is asserted. The UPWAIT signal becomes de-asserted when the DTACK\* signal is asserted by the MC68000 peripheral. Figures 1-1 and 1-3 show the complete interface and timing diagram.

**UPWAIT** =  $(CS^* \bullet DTACK^*)^* = CS + DTACK$

Figure 2. MPC860 Interface with Generic 68K Bus Timing Diagram