ATARI ® MegaSTe ® Service Manual

> Part Number: C302016-001 Revision A June 1991 Réf. 80047

#### Copyright© 1991, Atari Corp. All Rights Reserved

Every reasonable effort has been made to ensure the accuracy of this manual; however, due to ongoing changes, Atari Corporation cannot guarantee the accuracy of this information after the date of publication and disclaims liability for changes, errors, or omissions.

These documents are for repair service information only. Part numbers are for reference only. Only parts on the current dealer parts list are available. No license is given for any use by the possession of these documents and may not be reproduced in any form without the written approval of Atari Corporation.

1

i

### **MEGASTE DIAGNOSTIC MANUAL RELEASE NOTES**

19

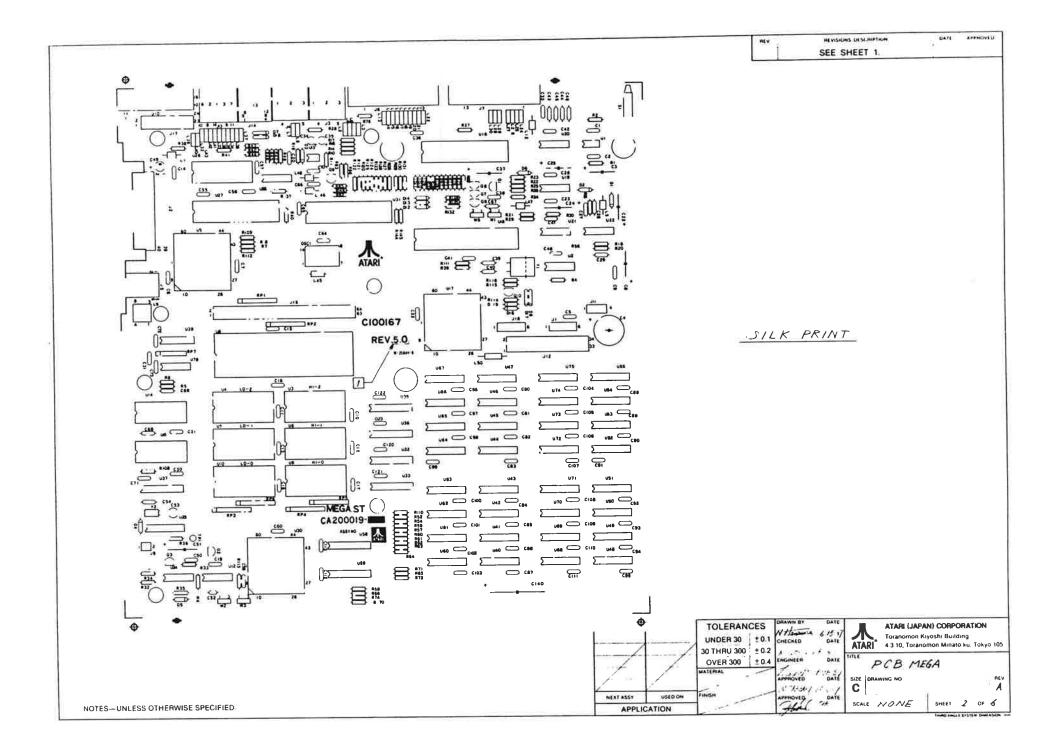

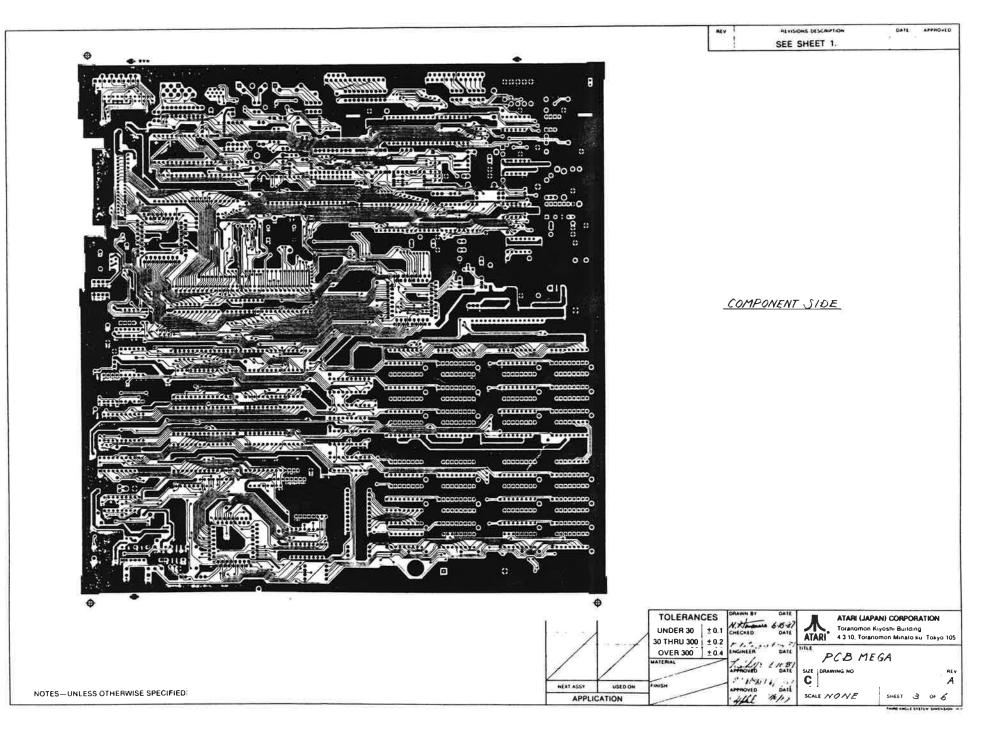

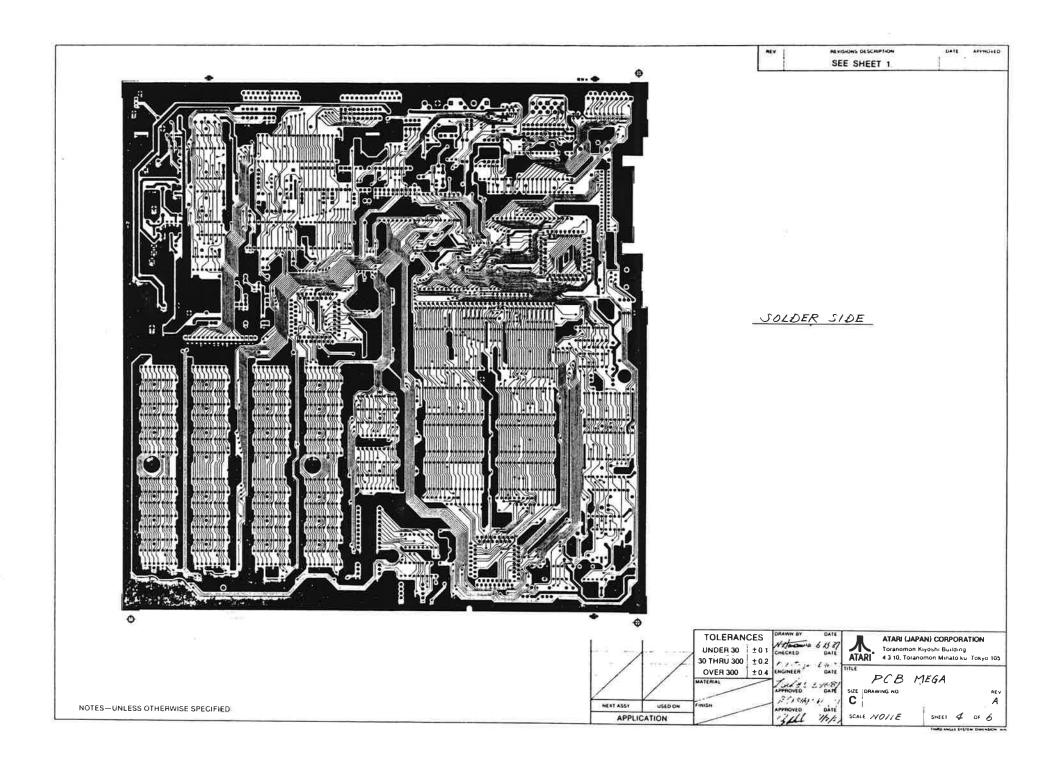

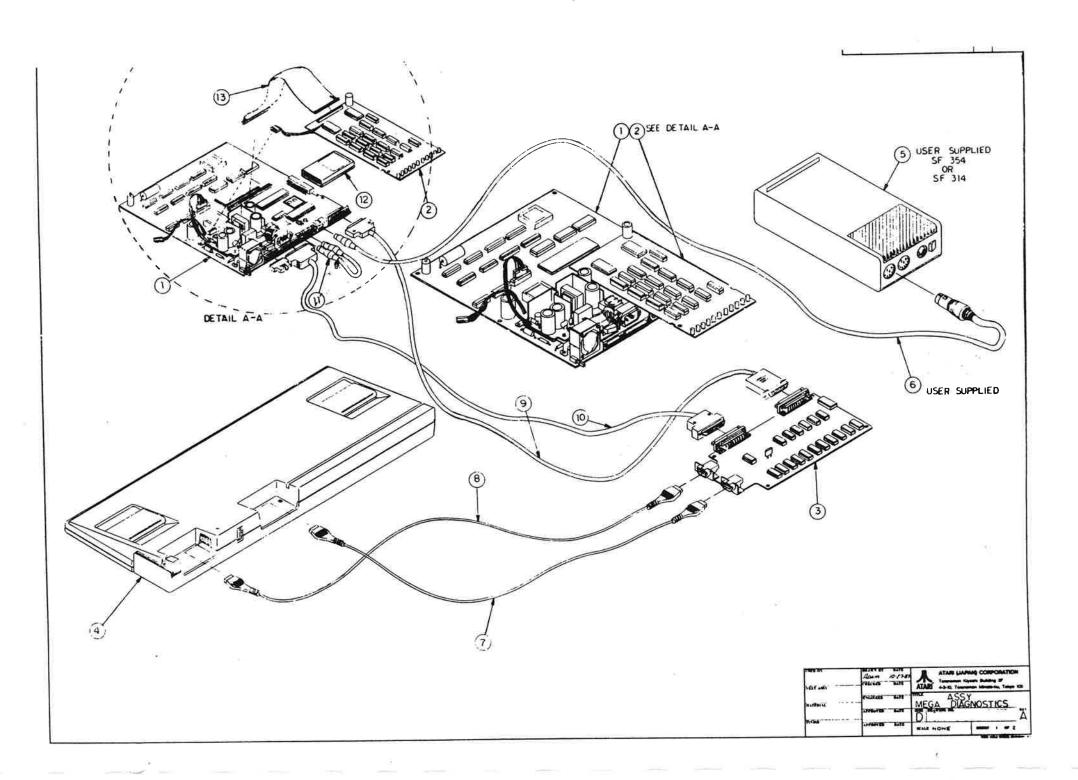

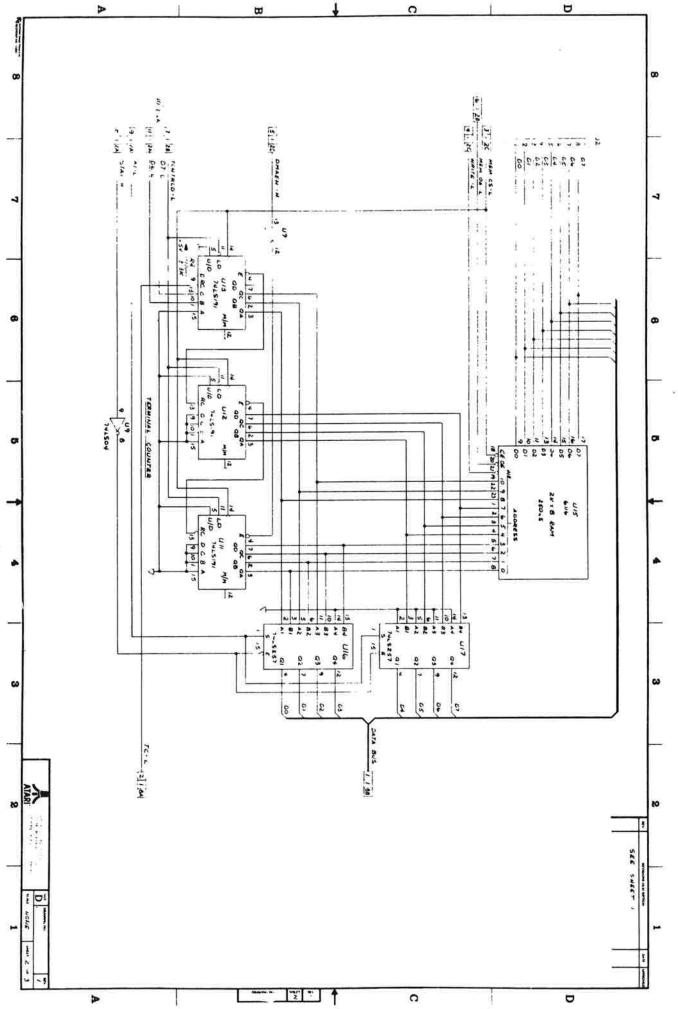

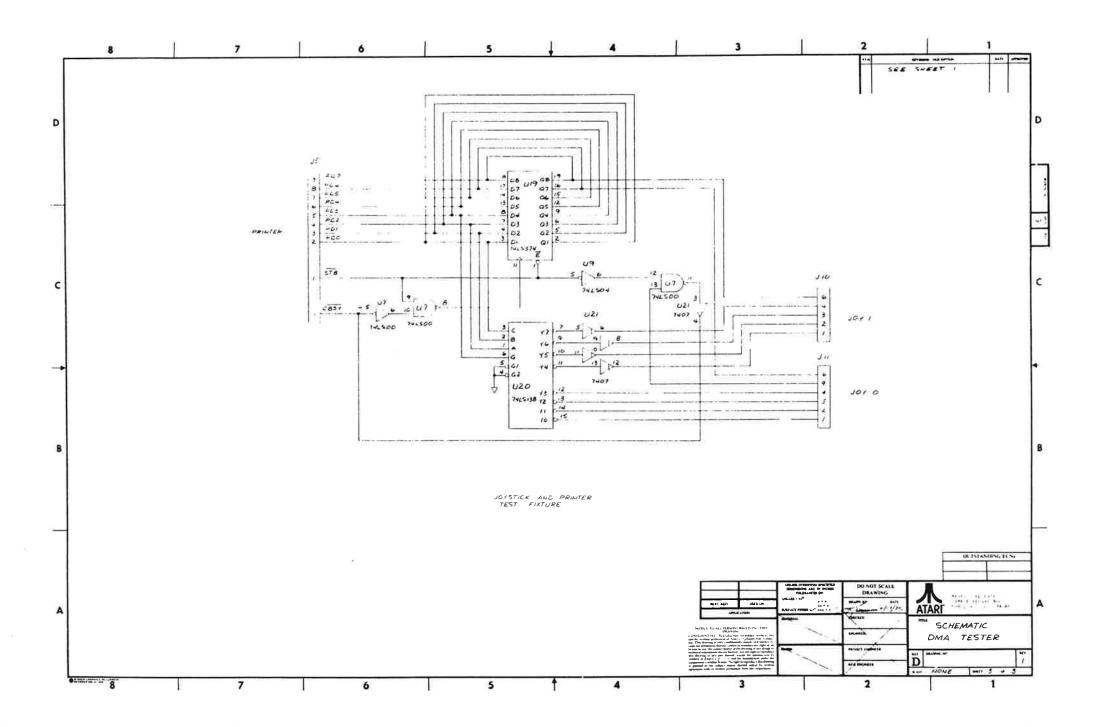

This is the first release of the MegaSTe Diagnostic Manual. At the time it was produced the Main PCB Assembly drawing (IPB) and the Test Configuration Setup drawing were not available. Photocopies of these drawings have been provided in the meantime until the actual drawings are complete. The new drawings will then be sent to each subsidiary to replace the existing photocopies.

#### CONTENTS

| SECTION ONE - INTRODUCTION              | 1. M. M.  |   |

|-----------------------------------------|-----------|---|

| Overview                                | 1.1       |   |

| Main Components                         | 1.2       | 1 |

| Case Design                             | 1.3       | , |

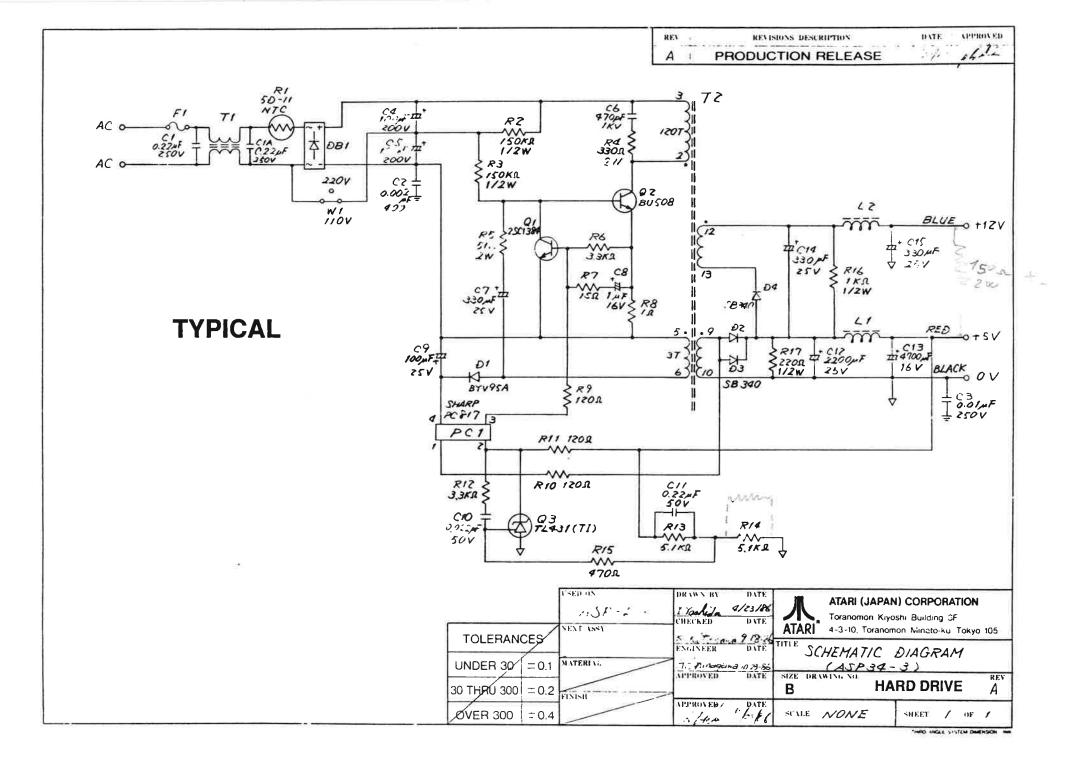

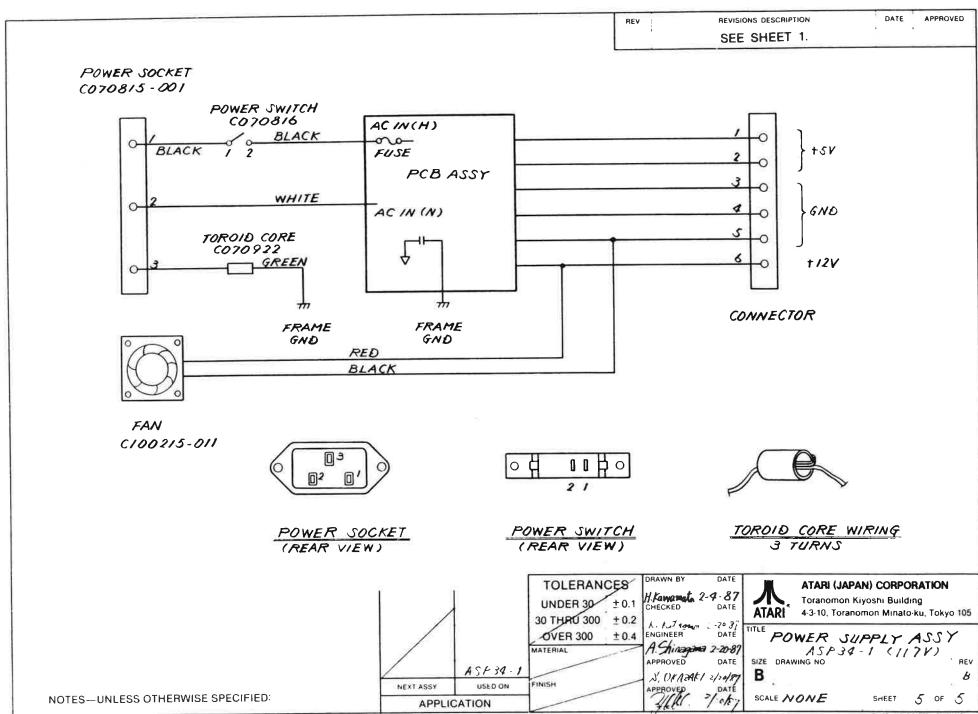

| Power Supply                            | 1.4       |   |

|                                         | _         |   |

| SECTION TWO - THEORY OF OPERATION       |           |   |

| Overview                                | 2.1       |   |

| Main System                             | 2.2       |   |

| Audio/Video subsystem                   | 2.3       | , |

| Input/Output subsystems                 | 2.4       |   |

| System Startup                          | 2.5       | ļ |

| System Errors                           | 2.6       |   |

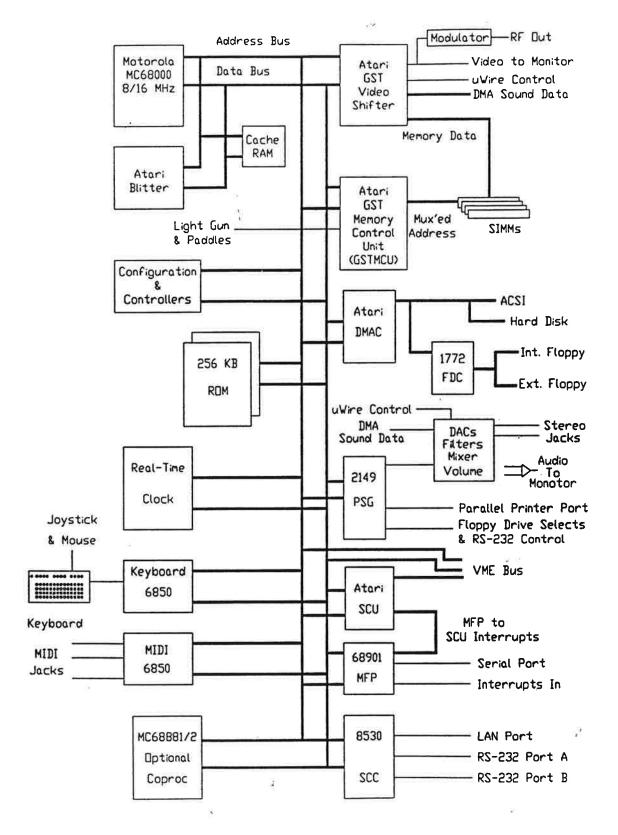

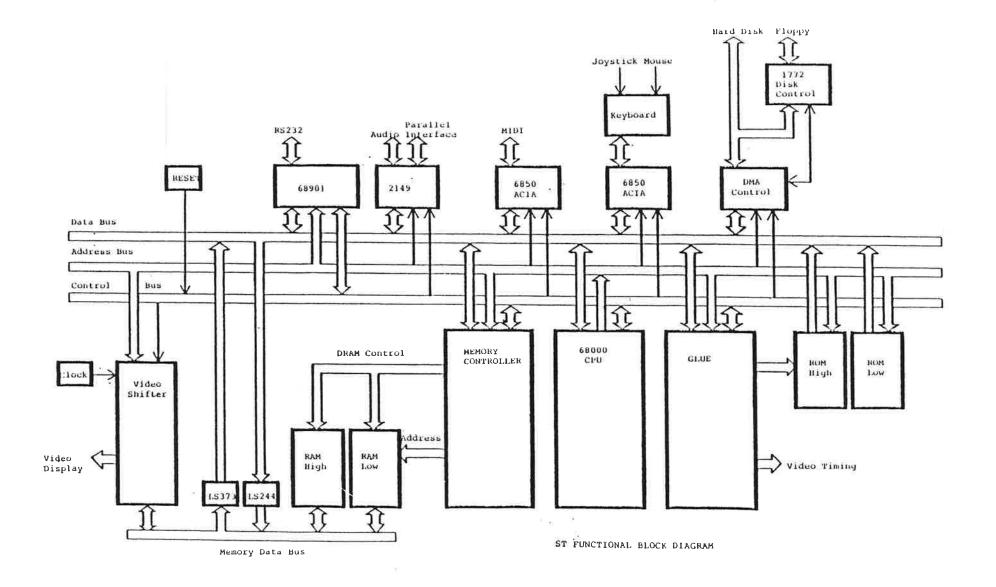

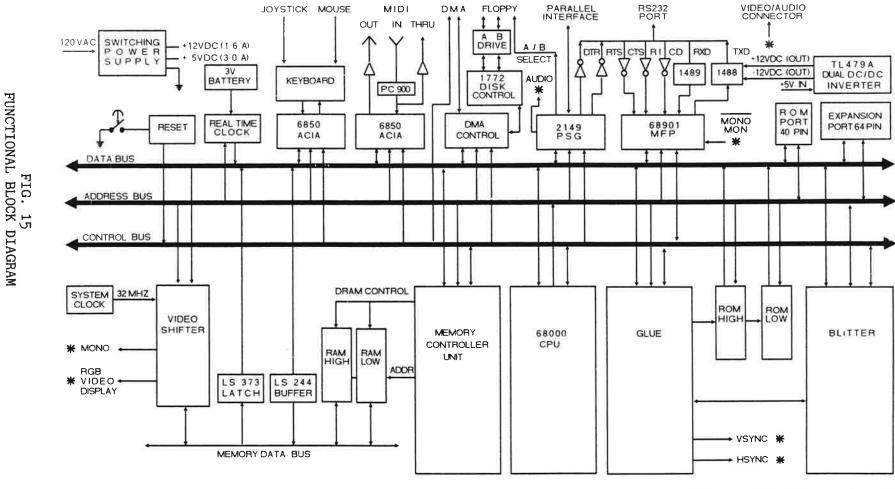

| Functional Block Diagram                | 2.7       |   |

| 0                                       |           |   |

| SECTION THREE - TESTING                 |           |   |

| Overview/Test Equipment                 | 3.1       |   |

| Test Configuration                      | 3.2       |   |

| Troubleshooting a Dead Unit             | 3.3       |   |

| Diagnostic Cartridge                    | 3.4       |   |

| Error Codes                             | 3.5       |   |

| Test Harness Hook-up Diagram            | 3.6       |   |

|                                         | 0.0       |   |

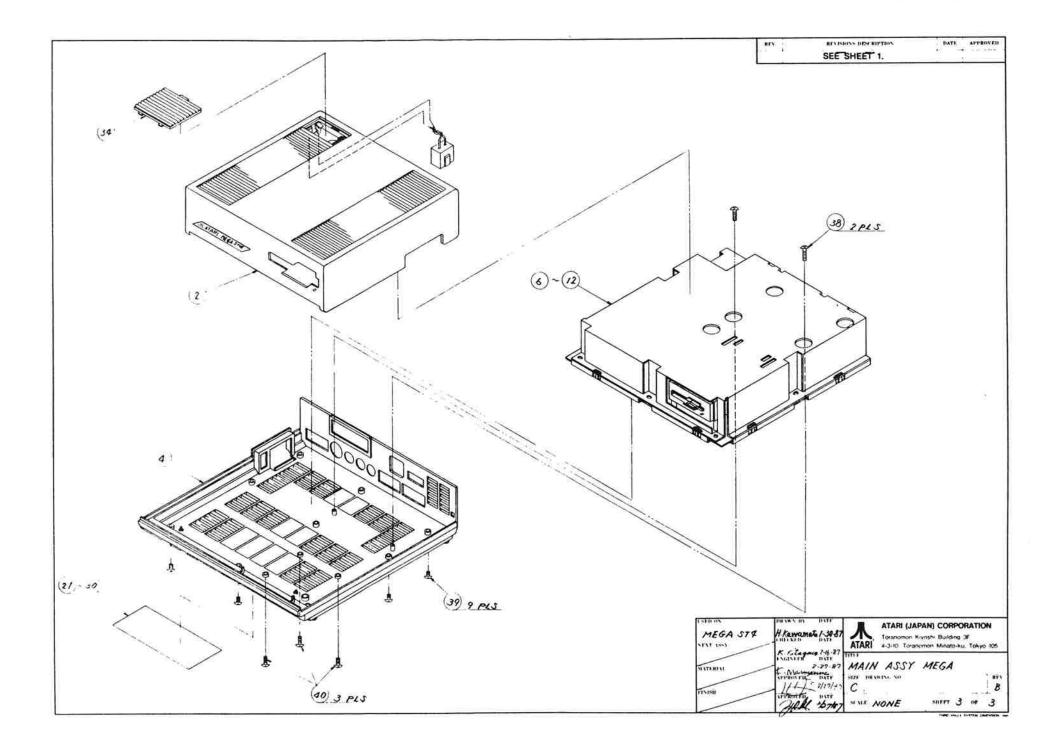

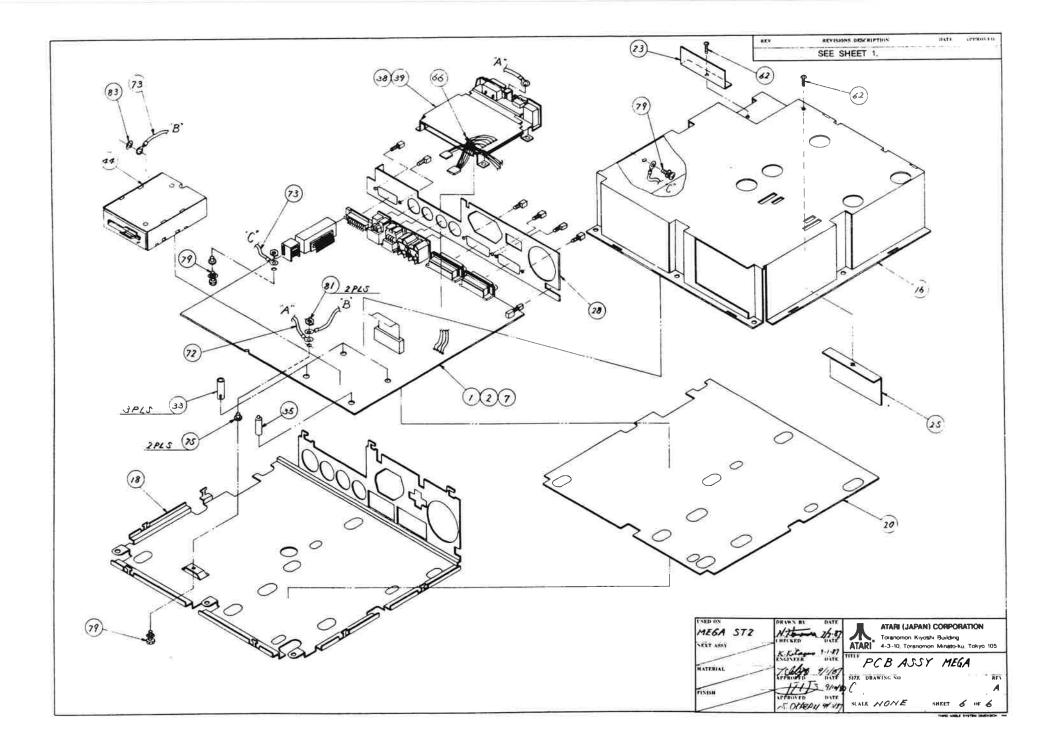

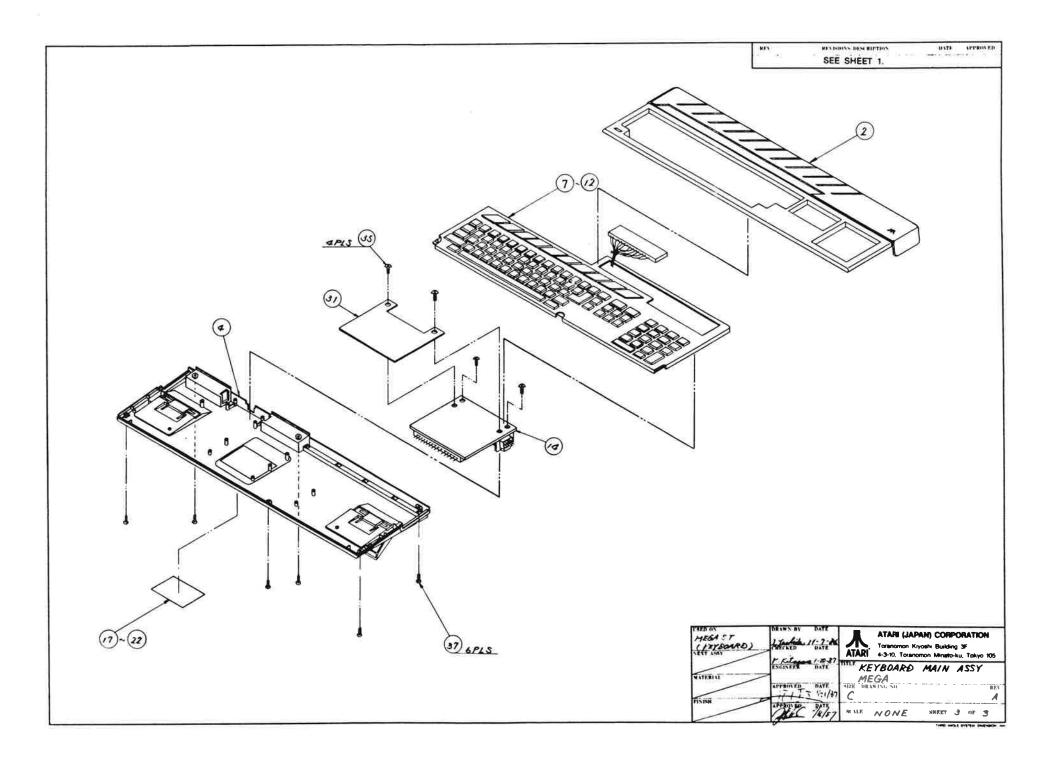

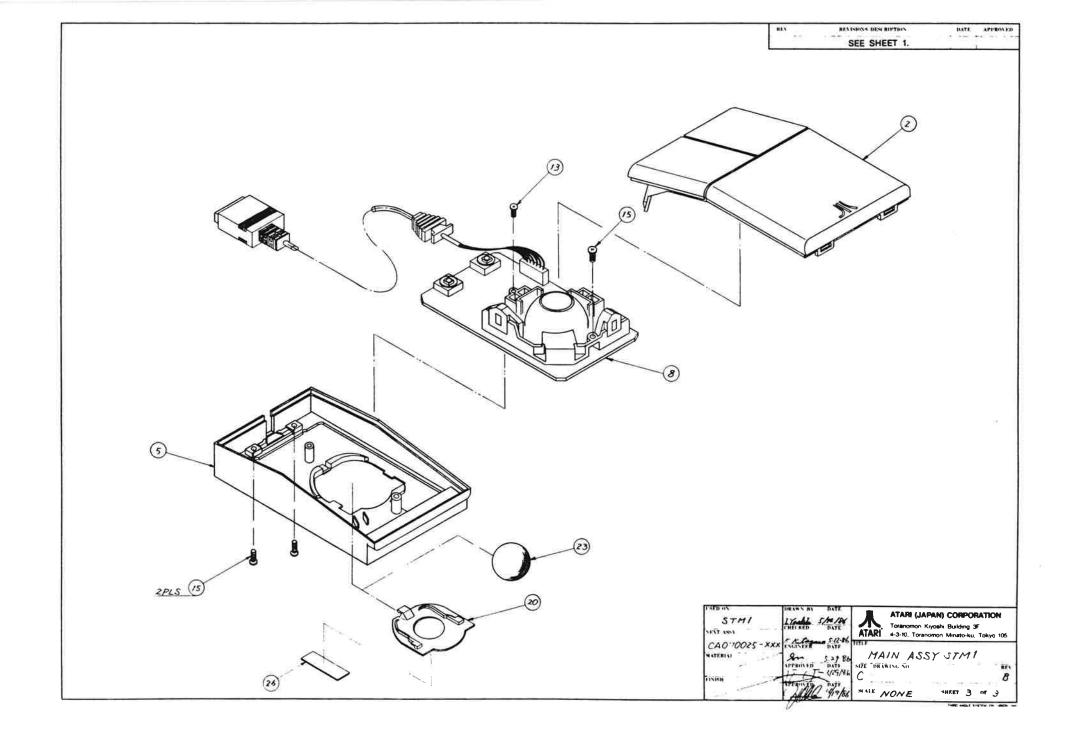

| SECTION FOUR - DISASSEMBLY/ASSEMBLY     |           |   |

| MegaSTe® Disassembly                    | 4.1       |   |

| MegaSTe® Assembly                       | 4.2       |   |

|                                         | 1.2       |   |

| SECTION FIVE - SYMPTOM CHECKLIST        |           |   |

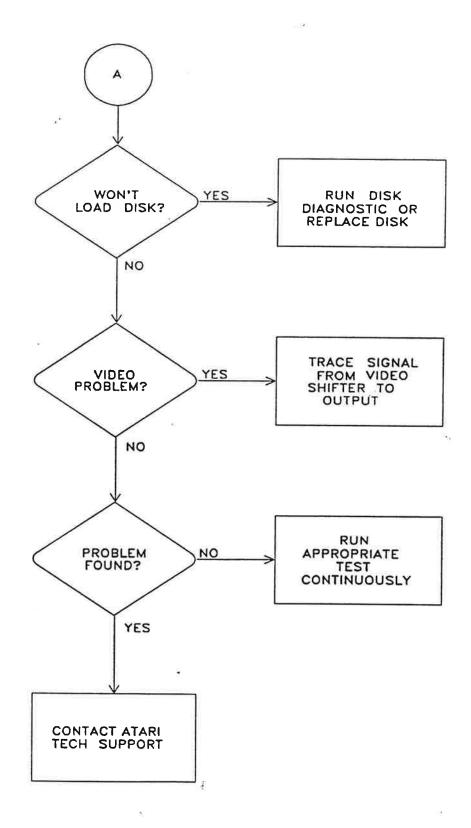

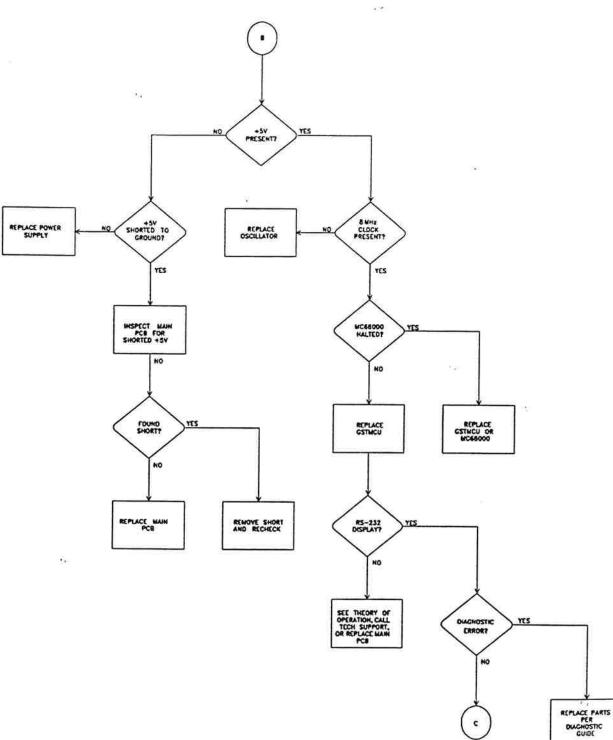

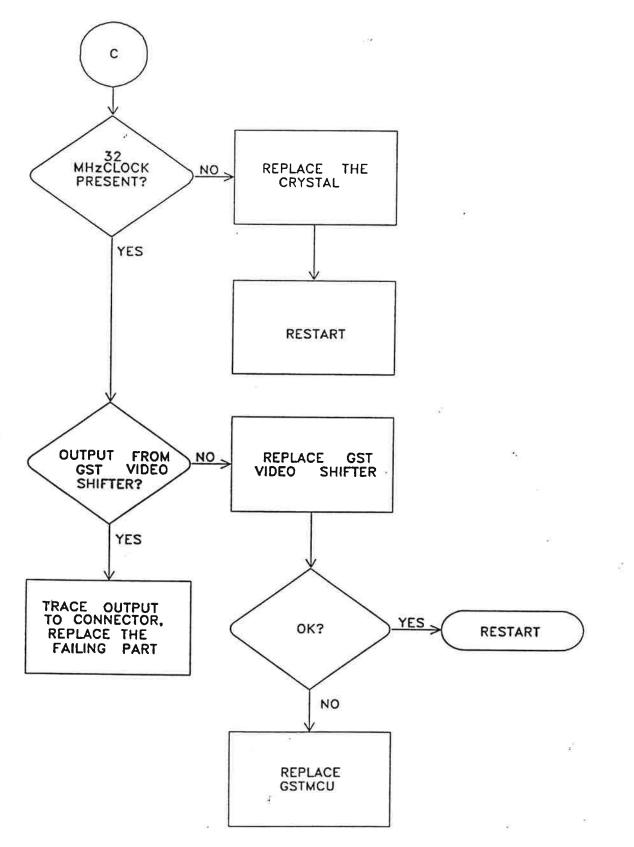

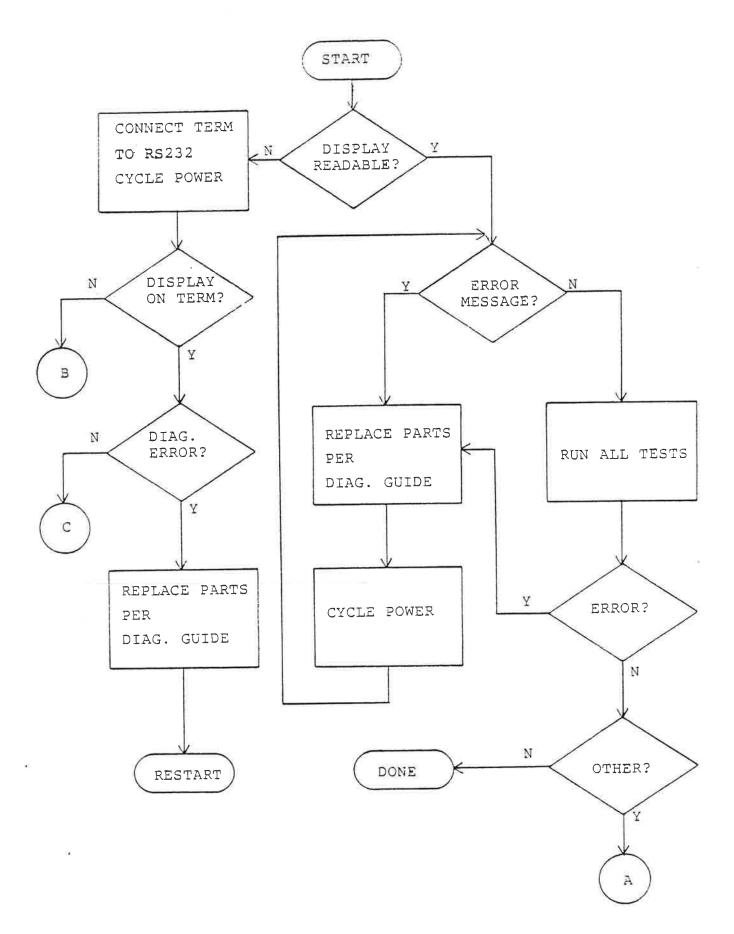

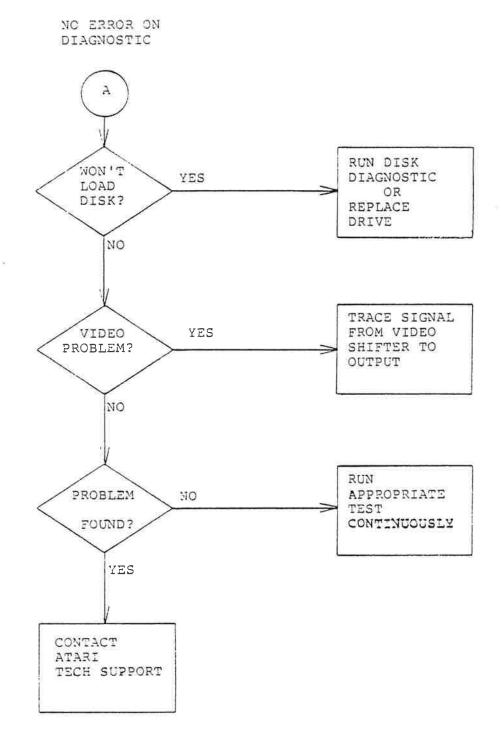

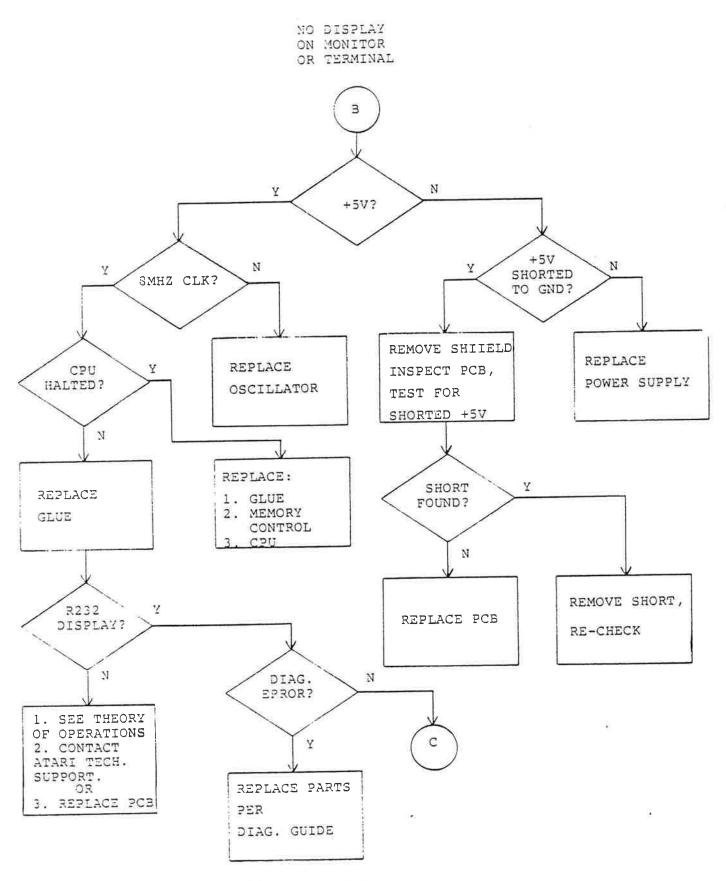

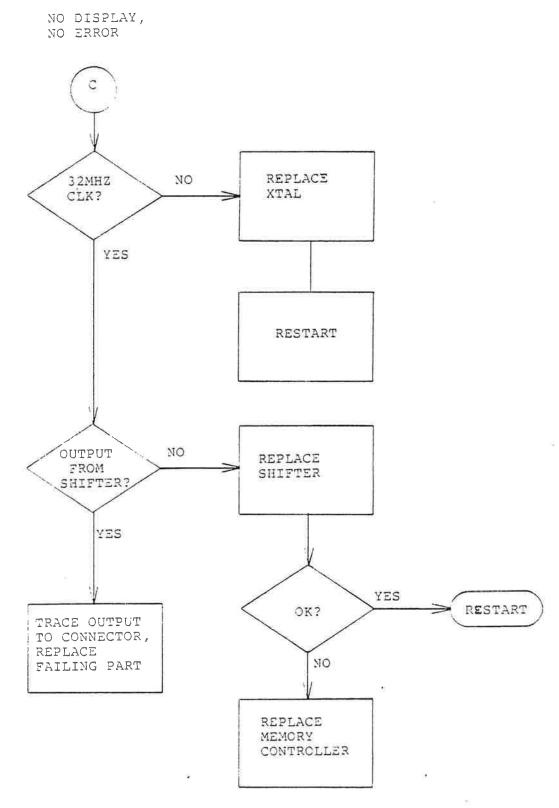

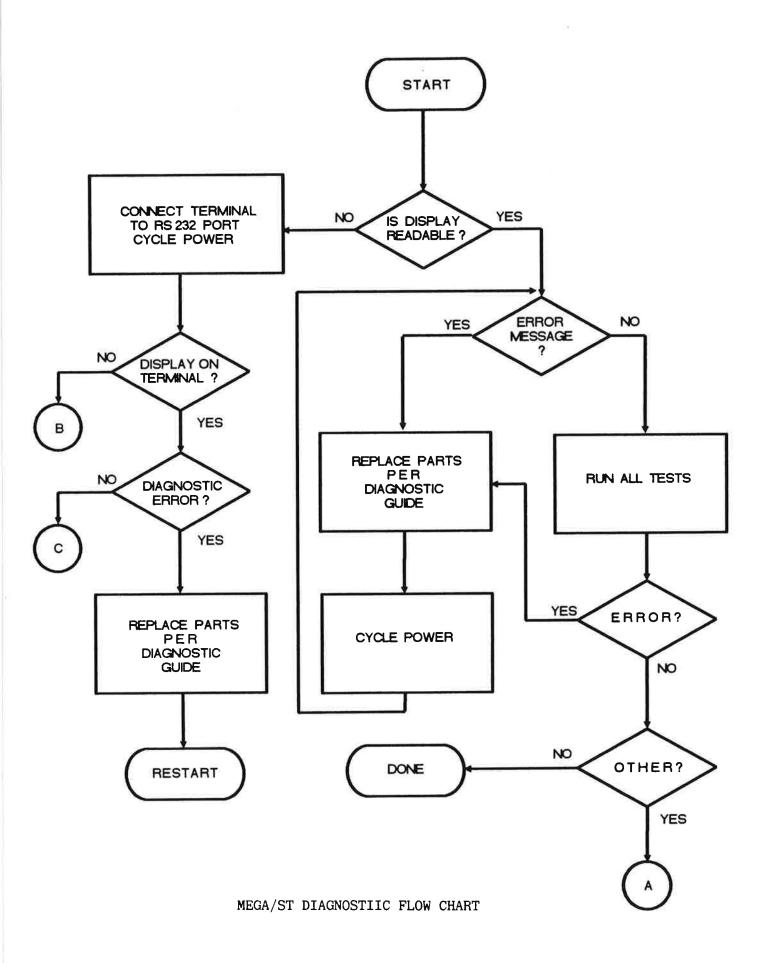

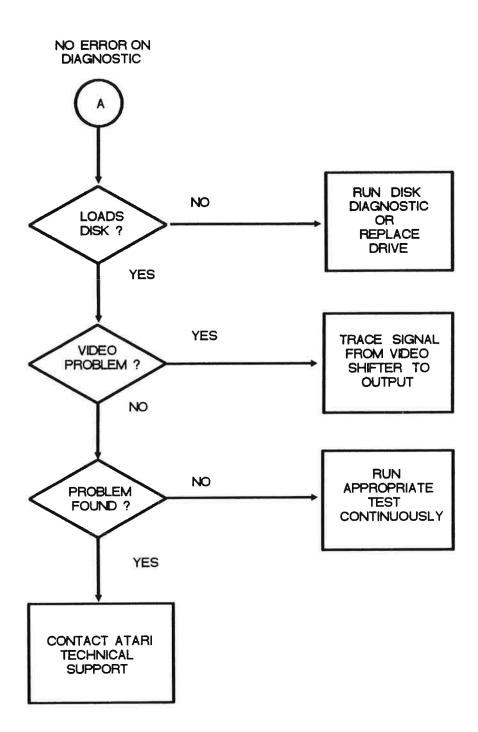

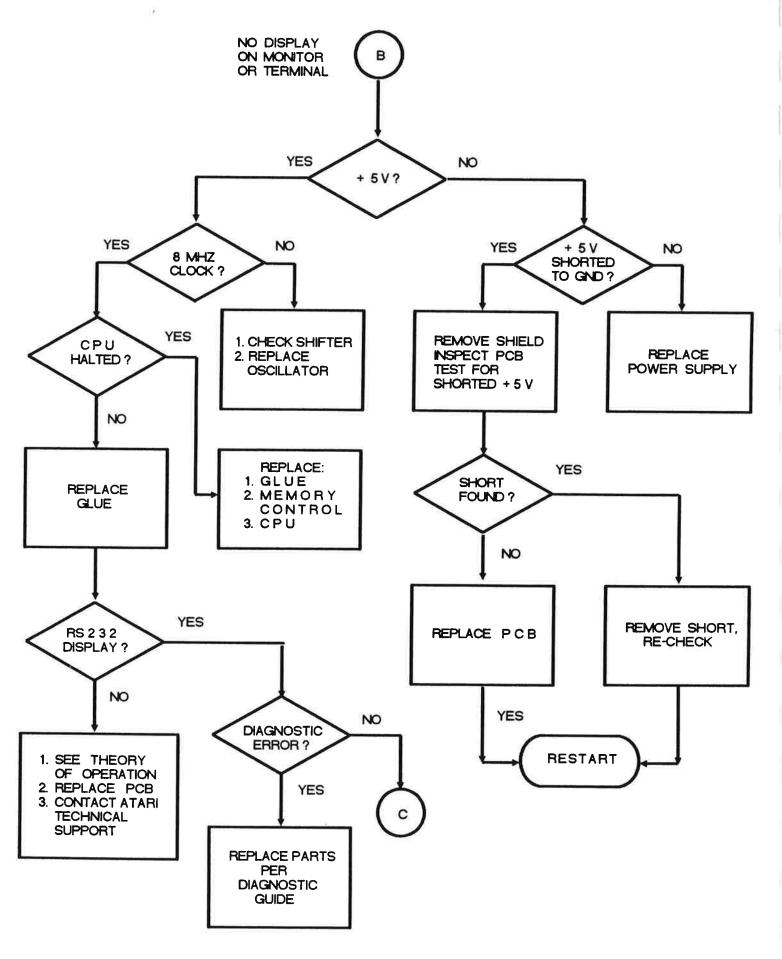

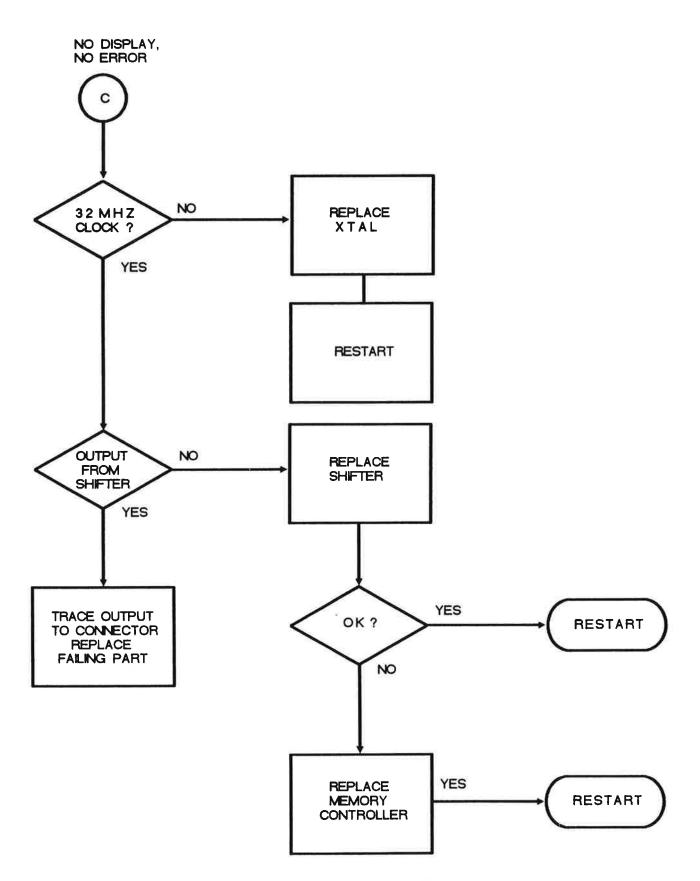

| SECTION SIX - DIAGNOSTIC FLOWCHART      |           |   |

|                                         |           |   |

| SECTION SEVEN - PARTS LIST AND ASSEMBL  | YDRAWINGS |   |

| SECTION EIGHT - SCHEMATICS AND PCB SILI | KSCREEN   |   |

|                                         |           |   |

SECTION NINE - GLOSSARY

# SECTION ONE

### **1.1 OVERVIEW**

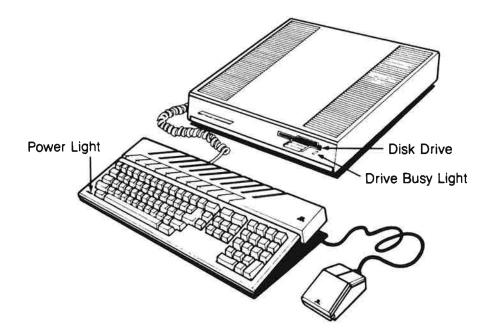

The Atari MegaSTe® is the newest enhancement in the series of Atari ST® computers. The MegaSTe® is upward compatible with the Atari STe® and is designed as an integrated unit with processor, memory, and I/O, floppy disk drive, and power supply in one package. The MegaSTe® provides either 1, 2, or 4 Mbytes of RAM memory and 256 Kbytes of ROM memory. A 16 Kbyte cache memory is also provided. The floppy disk drive storage capacity is 720 Kbyte (formatted). An optional 1.44 Mbyte (formatted) floppy, hard disk drive, and floating point coprocessor can also be added.

1

### **1.2 MAIN COMPONENTS**

### MAIN BOARD

- Power Supply

- Floppy Disk Drive

- Optional Hard Disk Drive

- Keyboard

ż

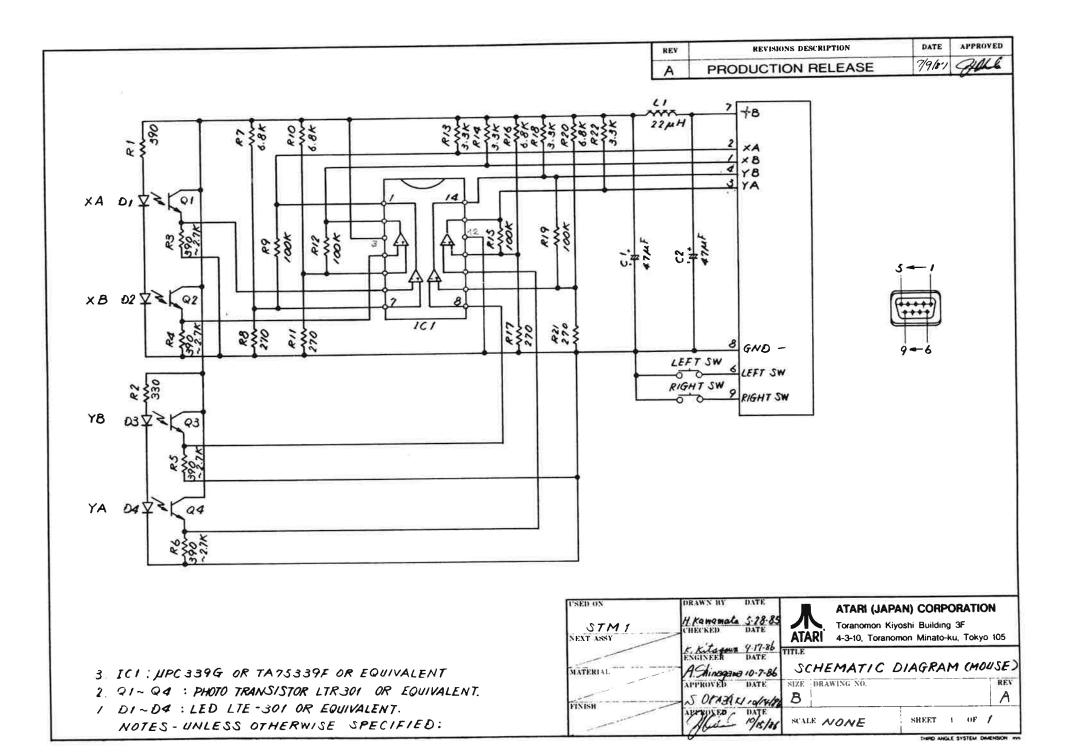

- Mouse

- Plastic Case (upper and lower)

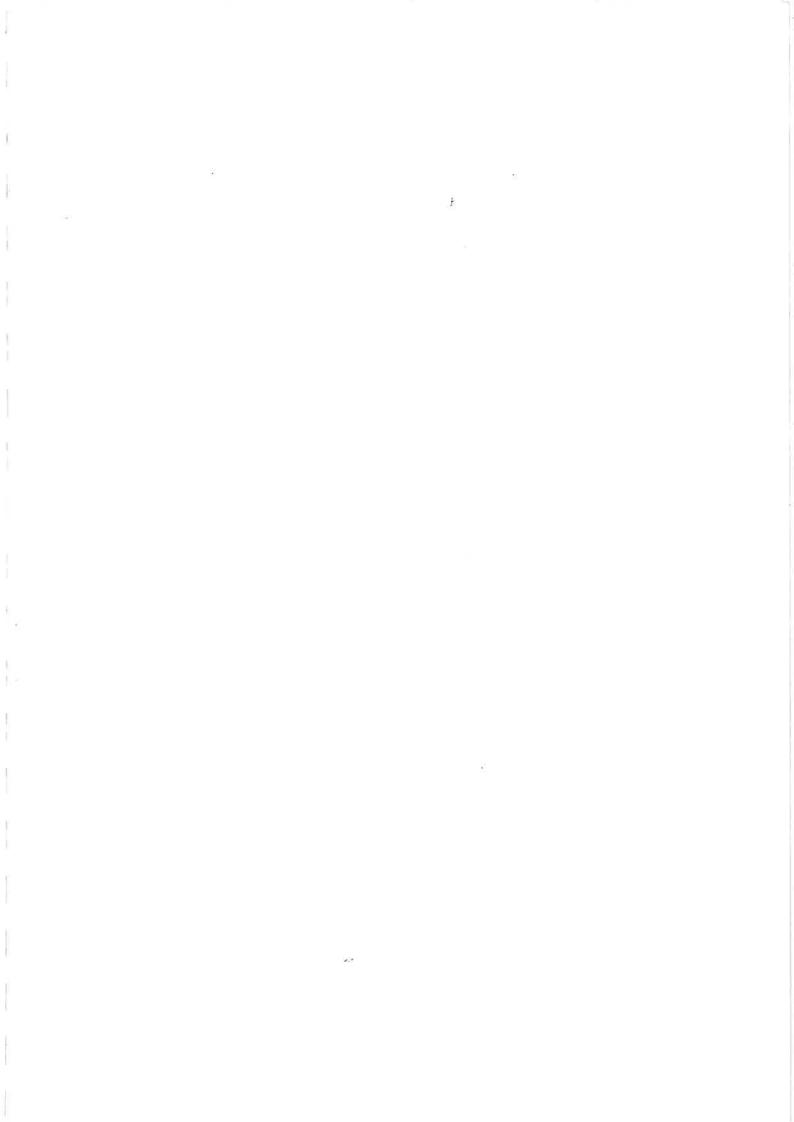

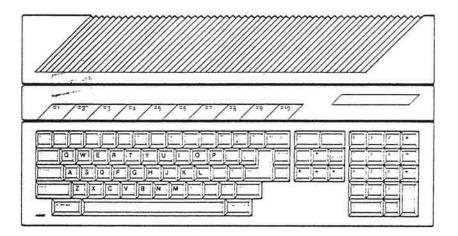

### **1.3 CASE DESIGN**

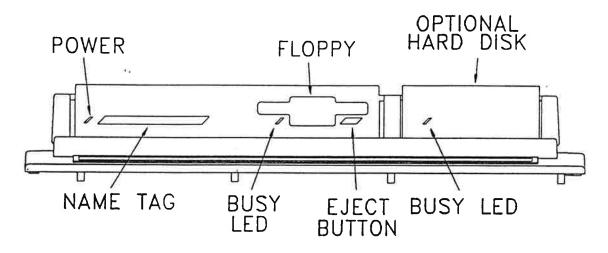

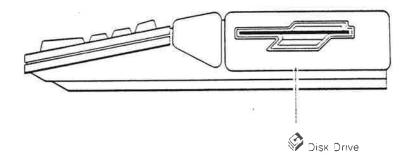

The front of the MegaSTe<sup>®</sup> contains the floppy disk drive with an eject button and busy LED. An optional hard disk can also be installed and contains its own busy LED.

#### FRONT VIEW

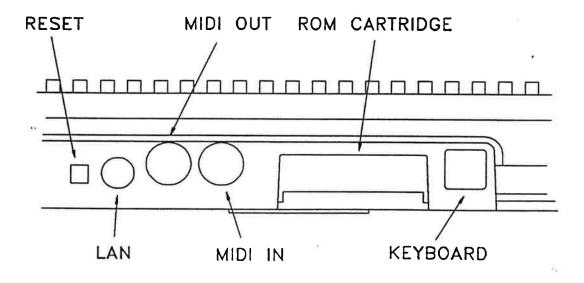

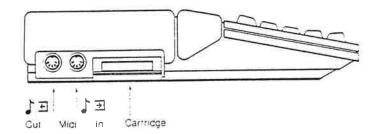

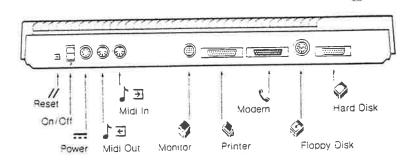

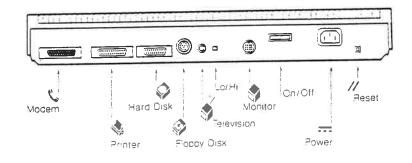

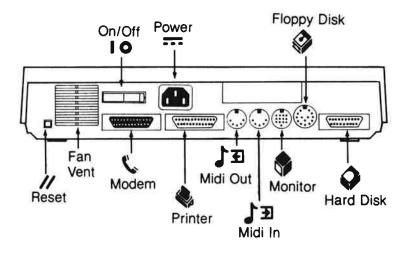

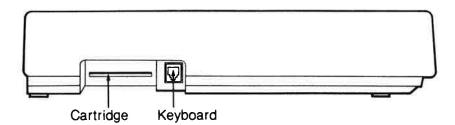

The left side of the MegaSTe® case contains the following items from left to right. Reset button, LAN connector, MIDI out jack, MIDI in jack, ROM cartridge port, and keyboard jack.

LEFT SIDE VIEW

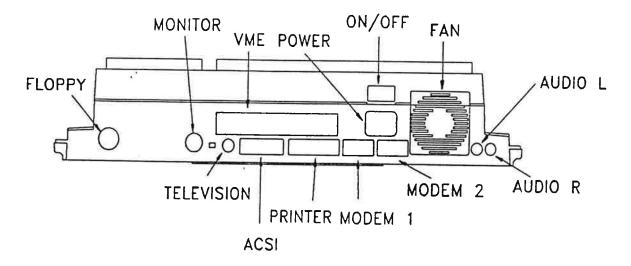

The rear of the MegaSTe® contains the following items from left to right. External floppy jack, monitor jack, TV jack, Serial 2 or VME slot, external ACSI interface connector, printer connector, modem 1 connector, on/off switch, power plug, modem 2 connector, fan, audio R connector, and audio L connector.

#### REAR VIEW

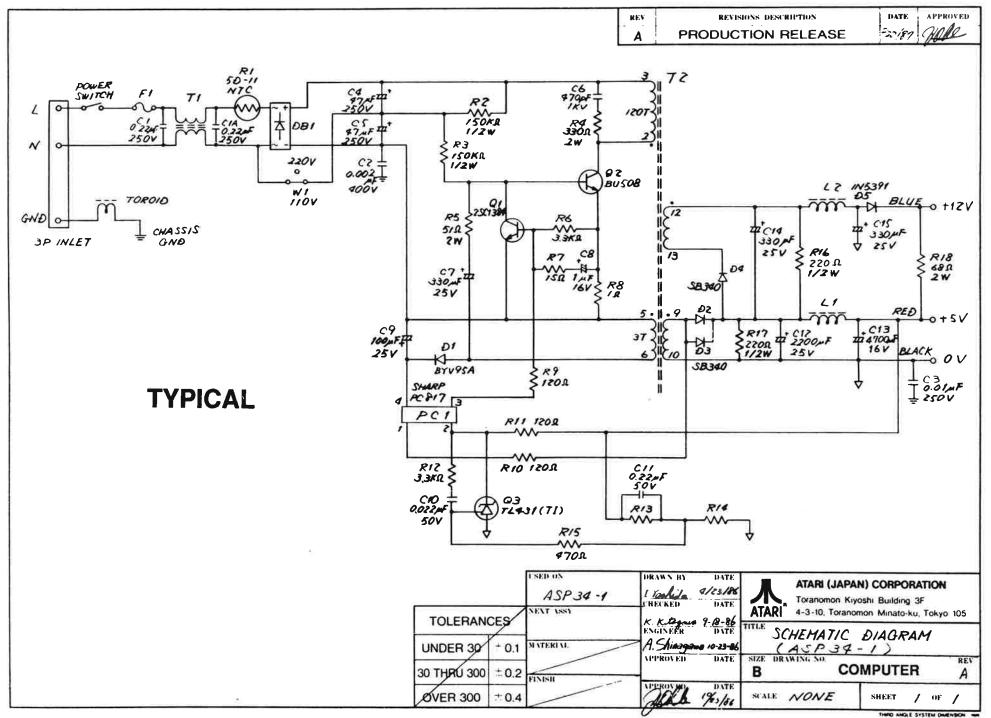

### **1.4 POWER SUPPLY**

### **1.4.1 POWER SUPPLY RATING**

The MegaSTe® has an integral switching power supply providing 65 watts of power. The supply can accept AC input of 100-240VAC at 2A, 50/60Hz. The power supply provides the following voltages and currents to the system:

| Voltage | Current |

|---------|---------|

| +5V     | 7A      |

| -5V     | 2A      |

| +12V    | 0.4A    |

| -12V    | 0.3A    |

3

### SECTION TWO

### THEORY OF OPERATION

#### 2.1 OVERVIEW

The MegaSTe® is an upward compatible extension of the Atari ST® architecture. A VME bus has been included in the MegaSTe® for expansion. The hardware is composed of a main system (central processing unit and support chips), audio/video subsystem, and several I/O subsystems.

Main System

- MC68000 processor running at 8/16 MHz

- Optional MC68881 or MC68882 coprocessor

- 256 Kbytes of ROM

- 1024, 2048 or 4096 Kbytes of RAM

- 16 Kbytes of cache RAM

- Processor speed / cache control

- Interrupt mask, status, and control (MFP and SCU)

- System timing and Bus control (GSTMCU, PALs U3, U6, U2)

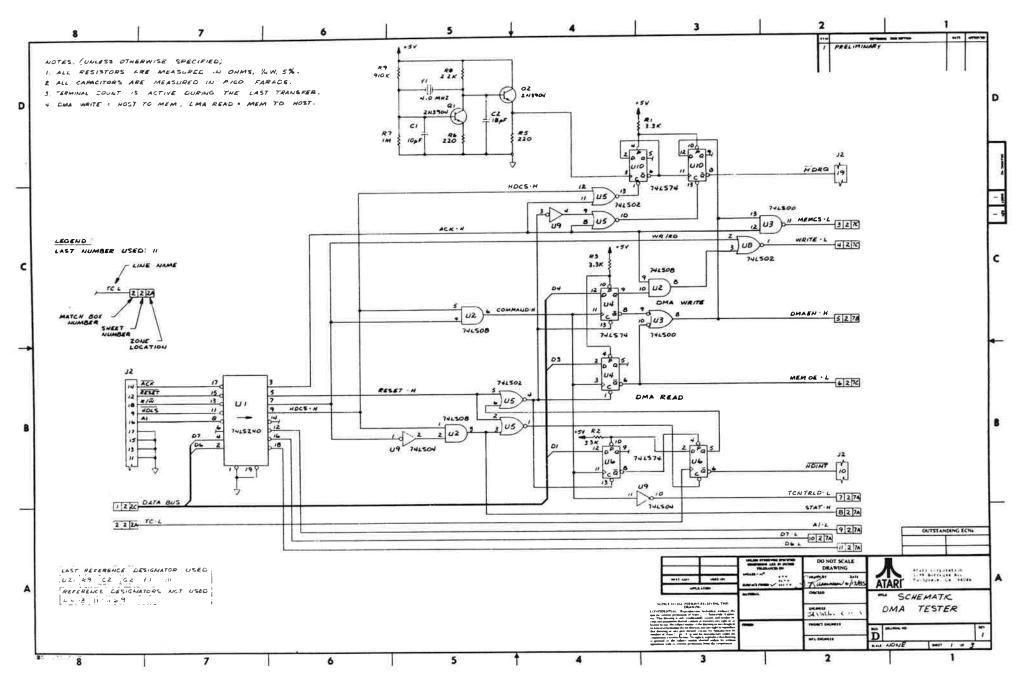

- DMA support

- Battery backed-up Real-time clock

#### Audio/Video Subsystem

- Bit Mapped video display using 32 Kbytes of RAM relocatable anywhere in memory. Three available display modes:

- 1. 320 X 200 16 out of 4096 colors

- 2. 640 X 200 4 out of 4096 colors

- 3. 640 X 400 monochrome

4

- Monitor interfaces include:

- 1. RGB

- 2. Monochrome

- 3. Composite

- 4. Television

- Audio outputs:

- 1. Programmable sound generator.

- 2. DMA sound output

#### I/O Subsystems

- Floppy disk interface

- High-speed serial ports

- MFP serial port

- Parallel printer interface

- Intelligent keyboard interface

- Mouse and Joystick interface

- Hard disk interface

- Musical Instrument Digital Interface (MIDI)

- VME bus

### **2.2 MAIN SYSTEM**

The hardware contained in the main system of the Atari MegaSTe® are the processor, optional coprocessor, ROM, RAM, cache RAM, system speed and cache control, Interrupt control (SCU and MFP), Timing and Bus control (GSTMCU), DMA support, Real-time clock, and ACSI interface.

### 2.2.1 PROCESSOR U007 PG. 1

The processor used in the Atari MegaSTe® system is a 16 MHz Motorola® MC68000 with a 32-bit internal architecture, 16-bit external data bus, and a 24-bit address bus. The processor can be operated at either 8 or 16 MHz.

#### 2.2.2 COPROCESSOR (OPTIONAL) UB02 PG. 11

A socket is provided in the MegaSTe® for an optional Motorola® MC68881 or high performance MC68882 floating point coprocessor. The coprocessor is clocked at 16 MHz independent of the speed at which the processor is running. The processor does not directly support the coprocessor but accesses it as an I/O device with memory type instructions via its address and data buses.

### 2.2.2.1 COPROCESSOR CONTROL SIGNAL GENERATION UB01 PG. 11

Chip select and data strobe signals for the coprocessor are generated by a PAL in location UB01.

#### 2.2.3 ROM U206, U207 PG. 2

The system contains two 128 Kbyte ROMs for a total of 256 Kbyte of access space. Since system bus access is 16-bits wide, both ROMs must be present for proper operation. Included in the tasks the ROM performs is system initialization and boot code from the floppy, hard disk, ACSI interface, and network. The ROM also contains a language specific implementation of the TOS operating system.

### 2.2.4 RAM U701, U702, U703, U704 PG. 7

The MegaSTe® includes either 1, 2, or 4 Mbytes of RAM used for both system and video. The RAM is implemented with 8-bit SIMMs (Single Inline Memory Module) and must be installed in matching pairs. Memory accesses to the RAM are interleaved between the Memory Controller and the Video Controller in 250ns time slices. During display cycles, the processor is prevented from accessing the RAM. However, the processor will be allotted the next 250ns time slice.

Additional memory can be installed in the system via VME memory cards. Up to 4 Mbytes of additional 16-bit wide RAM can be installed in this way. VME memory will typically run slower than on-board system memory because all accesses incur an additional wait state.

RAM memory map:

| Address         | Usage                             |

|-----------------|-----------------------------------|

| 000008 - 000800 | System memory (privileged access) |

| 000800 - 07FFFF | Low Bank (1 Mbyte systems)        |

| 080000 - 0FFFFF | High Bank (1 Mbyte systems)       |

| 000800 - 0FFFFF | Low Bank (2 Mbyte systems)        |

| 100000 - 1FFFFF | High Bank (2 Mbyte systems)       |

| 000800 - 1FFFFF | Low bank (4 Mbyte systems)        |

| 1FFFFF - 3FFFFF | High bank (4 Mbyte systems)       |

### 2.2.5 CACHE RAM U004, U005, U008, U009 PG. 1

Cache RAM consists of 16 Kbytes of fast SRAM memory. RAM cycles are cached using 8K words, which are 16-bits wide. This permits cache-hit memory cycles to run at zero wait states and without taking a cycle on the system bus when the processor is running at 16 MHz.

### 2.2.6 SYSTEM CONTROL UNIT (SCU) U801 PG. 8

The SCU provides several system support functions including interrupt masking and status reporting, interrupt generation, and bus timeout detection.

### 2.2.6.1 INTERRUPT MASK AND CURRENT STATUS

The SCU contains two registers used to mask interrupts to the processor. These registers, in effect, screen the interrupts from both main system devices and VME bus devices and present them, when enabled (not masked), to the processor. Masked interrupts (not enabled) are not presented and therefore not seen by the processor. These registers are cleared at power up or reset, disabling all interrupts.

The SCU also contains a register which latches the current state of the seven interrupt request levels from each one of the sources. This register shows the state of the interrupt lines before they are ANDed with the mask registers.

\$

#### **2.2.6.2 INTERRUPT GENERATION**

The system can write to an I/O address to generate a level 1 autovectored interrupt to the processor. The SCU is hardwired to the following interrupt scheme:

- Only interrupt levels 5 and 6 have external interrupt acknowledge (IACK) pins and are capable of generating vectored interrupts to the system.

- SCU generated interrupts IRQ1 and IRQ3 are hardwired to the corresponding priorities and are always autovectored.

- The VMEbus ACFAIL generates an IRQ7 interrupt to the processor. The only other source of IRQ7 interrupt is from a VMEbus card.

#### 2.2.6.3 BUS TIMER

The SCU implements a bus timer so that if a bus cycle is not terminated within 16us, the SCU will generate a bus error signal.

### 2.2.6.4 PROCESSOR/CACHE CONTROL

There is a register implemented in the SCU used to select processor speed (8/16 MHz) and enable cache memory. The address decode for the register is done by PAL UA02 (Pg. 10). Bit 0 enables the cache and bit 1 selects the processor speed. The clock control signal is generated by PAL U407 (Pg. 4) and supplied to PAL U11 (Pg. 1). The cache enable signal is also supplied to PAL U11. These signals are the multiplexed to the processor clock pin and cache enable pins of the SRAM by PAL U12 (Pg. 1).

### 2.2.7 68901 MFP U306 PG. 3

### 2.2.7.1 MFP INTERRUPT CONTROL

The 68901 MFP handles up to 16 interrupts. Currently all but one are used. Each interrupt can be masked off or disabled by programming the MFP. The 8 inputs are also directly readable by the CPU. When the MFP receives an interrupt input, or generates an input internally, if the interrupt is enabled, MPINT will be driven low. When the CPU is ready to respond, it signals interrupt acknowledge (PC0-PC2 high and VMA low) and GSTMCU will assert IACK (interrupt acknowledge). The MFP will assert DTACK and put a vector number on the data bus, which the CPU will read and use to calculate the address of the interrupt routine.

t

١

The interrupts controlled by the MFP are: monochrome monitor detect (MONOMON), RS-232 (Including CTS, DCD, and RI), floppy and hard disk (FDINT and HDINT respectively), parallel port BUSY, display enable (DE, which equals the start of the display line), 6850 IRQ's for keyboard and MIDI data, and MFP timers.

Not all I/O operations are interrupts. The CPU can also poll the MFP while waiting for an operation to complete. The MFP also contains four timers. These are used by the Operating System for event timing and by the RS-232 port for transmit and receive clocks.

#### 2.2.8 SYSTEM TIMING AND BUS CONTROL GSTMCU U501 PG. 5 PALS U2, U3, AND U6 PG. 11

The GSTMCU is an integral part of the system and is involved in almost every operation in the computer. The functions performed by the GSTMCU include clock dividers, video timing, signal and bus arbitration, memory control, and chip selects.

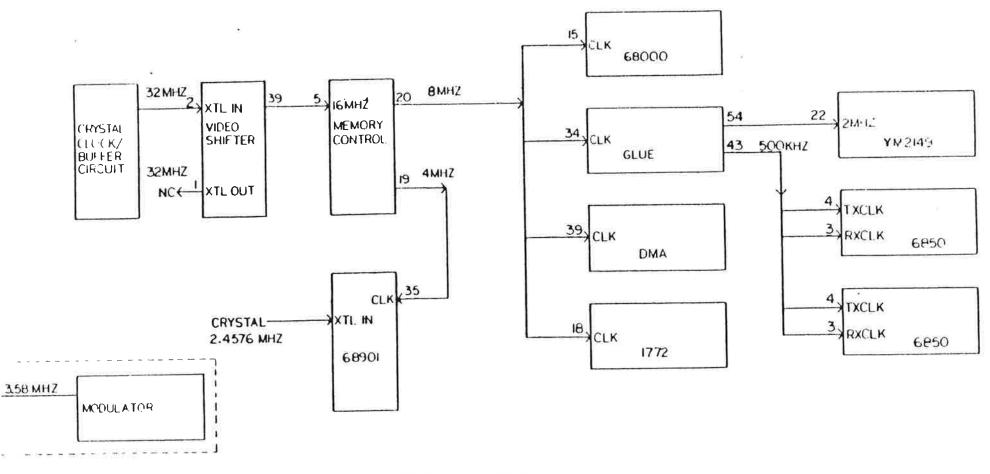

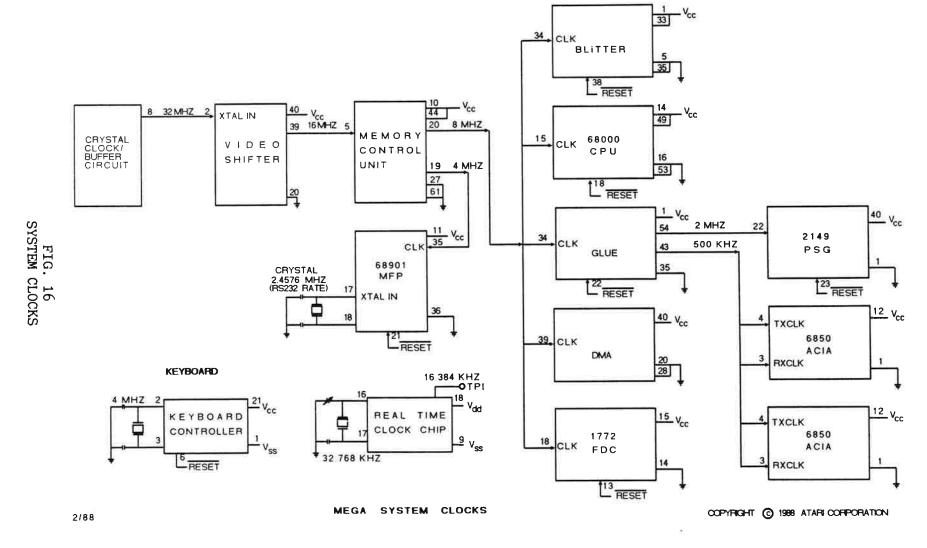

#### 2.2.8.1 CLOCK DIVIDERS

The clock dividers within the GSTMCU are used to take the 16 MHz input and divide it into 4 MHz, 8 MHz, and 500 kHz clocks for use by other devices in the system.

#### 2.2.8.2 VIDEO TIMING

The GSTMCU outputs the signals BLANK, DE (Display Enable), VSYNC, and HSYNC to generate system video. There is also a read/write register within the GSTMCU which is used to configure for 50, 60, or 71 Hz monitor operation (done by software).

#### 2.2.8.3 SIGNAL AND BUS ARBITRATION

The GSTMCU arbitrates the bus during DMA cycles to prevent the processor and DMA controller from interfering with one another. PAL U6 synchronizes the bus error and data transfer acknowledge signals to the processor. PAL U3 is a data strobe state machine used to generate both upper and lower data strobes on byte reads when cache RAM is enabled. PAL U2 is used to latch latch data strobe, address strobe, and read/write signals to the processor.

4

#### 2.2.8.4 MEMORY CONTROL

The GSTMCU takes addresses from the address bus and coverts them to Row Address Strobe (RAS) and Column Address Strobe (CAS) signals to control all RAM accesses. The Memory Controller internal to this device is also responsible for refreshing the DRAM (dynamic RAM), loading the Video Shifter with display data, and sending or receiving data during DMA cycles.

#### 2.2.8.5 CHIP SELECTS

The GSTMCU decodes addresses and generates chip selects to the 6850's, 68901 MFP, DMA Controller, Programmable Sound Generator, internal Memory Controller, and ROMs. It receives signals from the MFP, DMA, and Memory Controller to synchronize data transfers. The GSTMCU also decodes the addresses necessary to enable the RAM and ROM.

#### 2.2.9 DMA SUPPORT U404 PG. 4

Direct memory access is provided to support both low speed (250 to 500 kilobits/sec) and high speed (up to 8 Megabits/sec) 8-bit device controllers. The floppy disk transfers at low speed and the hard disk (or other devices on the hard disk port) transfer at high speed.

For DMA to take place, the Memory Controller is given the address of where to take data from or put data in RAM, the DMA Controller is set up (with channel, high or low speed, and how many bytes) and the peripheral is given a command to send or receive data.

The entire block of data (the size must be given to the DMA Controller and the peripheral before the operation starts) is then transferred to or from memory without an intervention by the CPU.

### 2.2.10 REAL-TIME CLOCK U402 PG. 4

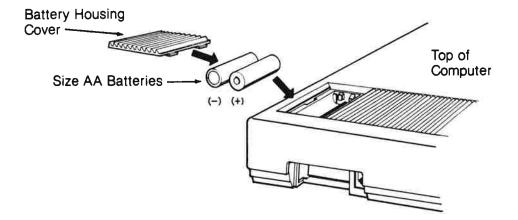

The MegaSTe® system includes a Real-time Clock chip. When the system is powered on the real-time clock is powered by the main PCB power supply. In the event of a power failure, or when the system is powered off, the real-time clock is powered by a 3.6v lithium battery. This allows the date and time to be maintained even when there is no power to the unit.

The real-time clock provides time of day (down to one second resolution) and date. The RTC is provided with a 32.760 kHz oscillator that is independent of all other system clocks. The chip is accessed through 32 4-bit registers accessed in two banks. Bank 0 allows reading and setting of each digit of the date and time. It also allows access to test and control registers within the device. Bank 1 allows setting the digits of the alarm function and controls the mode of operation of the clock.

### 2.3 AUDIO/VIDEO SUBSYSTEM

### 2.3.1 VIDEO SUBSYSTEM U501, U502, U205, U503 PG. 5

The video subsystem consists of the video display memory (an arbitrary block of RAM starting on any word boundary), the GSTMCU U501, a graphics control chip GSTSHFTR U502, a graphics coprocessor chip STB U205, some discrete components to drive the video output, and an RF modulator U503. The role of the GSTMCU has already been covered in section 2.2.8.2

### 2.3.1.1 GSTSHFTR VIDEO SHIFTER U502 PG. 5

There are 16 color palette registers in the shifter. All 16 may be used in low resolution (320 X 200). Four may be used in medium resolution (640 X 200), and one may be used in monochrome (640 X 400) high resolution (actually only bit 0 of register 0 is used for inverse/normal video). Contained in each entry are twelve-bits of color; four-bits each for red, green, and blue. Therefore there are 16 X 16 X 16 or 4096 colors possible for each entry. For a given pixel, the color which is displayed is taken from the palette referred to by getting information from each logical plane (see the description of video display in section 2.3.1.3). The shifter will output the red, blue, and green levels specified by that palette.

Note that there are four outputs for each color. Each output is either on or off. This makes the number of possible output levels 2 to the 4th power or 16. The four outputs are summed through a resistor network to proportion the voltage level to give sixteen equal steps. In monochrome mode, the color palettes are bypassed and there is a separate output.

### 2.3.1.2 GRAPHICS COPROCESSOR STB U205 PG. 2

The graphics coprocessor (Blitter) handles the extra burden of graphics video generation on the processor. The STB performs bit aligned block transfers required in graphics generation, adding to the capability of the processor which only works on word or byte boundaries. The STB also provides barrel shift functions that are not contained in the processor.

#### 2.3.1.3 VIDEO DISPLAY MEMORY

Display memory is part of main memory with the physical screen origin located at the top left corner of the screen. Display memory is configured as 1, 2, or 4 logical planes interwoven by 16-bit words into contiguous memory to form one 32,000 byte physical plane starting at any 2-byte boundary. The starting address of display memory is placed in the Memory Controller's Video Base High, Video Base Mid, and Video Base Low registers by the Operating System or application. This register is loaded into the Video Address counter (high, mid, and low) at the beginning of each frame. The address counter is incremented as the Bit Map planes are read.

The Memory Controller will load display information into the Video Shifter 16 bits at a time, and the Video Shifter will decode this information to generate a serial display stream. In monochrome mode, each bit represents one pixel on or off. In color, bits are combined from each plane to generate the correct level of red, green, and blue.

For example, in low resolution (4 planes) four words are loaded into the Video Shifter for each word (16 pixels) displayed on the screen. The Video Shifter combines bit 0 from each word to form a four bit number (0-15), and takes the color from the palette referenced by that number (e.g. 0101 = 5, use color from palette register 5) and outputs those levels, then takes bit 1 from each plane and outputs the color from the palette referenced by those four bits, etc.

#### 2.3.1.4 TELEVISION INTERFACE PG. 5

The MC1377 takes the red, green, and blue video signals from the emitter followers Q501, Q502, and Q503 and adds them to the HSYNC and VSYNC signals to form composite video. The composite signal is then modulated onto an RF carrier and locked onto the color burst frequency by a phase locked loop. The RF video is then output to an RCA type jack on the back of the computer.

#### 2.3.1.5 HORIZONTAL SCROLLING

Two additional registers implement a horizontal smooth scroll capability. The horizontal pixel scroll register holds a pixel offset value from 0-15 at which to begin display. Increasing this value by one will scroll the whole display one pixel to the left. The extra line width register contains a number of words that is added to the ending address of each display line to get the beginning address of the next display line. It puts an undisplayed area to the right of the video screen. By using these two registers the video screen can be used as a horizontally scrolling window.

#### 2.3.1.6 GENLOCK AND THE MEGASTE®

The MegaSTe® has the ability to accept external sync. This was done to allow synchronization of the MegaSTe® video with an external source. In order to do this reliably, the system clock must also be phase-locked to the input sync signal. To do this pin three of the monitor connector must be grounded. The clock can then be input on pin four of the monitor connector. The internal frequency of this clock is 32.215905 MHz for NTSC and 32.084988 MHz for PAL.

#### 2.3.1.7 MONITOR INPUT LEVELS

HSYNC - TTL level, negative, 3.3 K ohm VSYNC - TTL level, negative, 3.3 K ohm Monochrome - digital 1.0V p-p, 75 ohm RGB - analog 0-1.0V p-p, 75 ohm Audio - 1.0V p-p, 1 K ohm

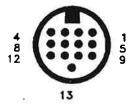

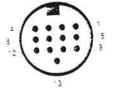

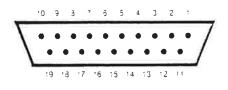

#### 2.3.1.7 MONITOR CONNECTOR

The video output is provided on a 13-pin DIN type connector located on the back of the computer. The connector is compatible with the ST® and STe® series systems. Either color or monochrome monitors can be used. The pinout of this connector is as follows:

<u>Pin</u> Function

- 1 Audio Out

- 2 Composite Video

- 3 External Clock Select (Pull low for external clock on pin 4)

- 4 Monochrome Monitor Detect (When used for GENLOCK becomes clock)

- 5 Audio Input

- 6 Green

- 7 Red

- 8 · Peritel Power

- 9 HSYNC

- 10 Blue

- 11 Monochrome Out

- 12 VSYNC

- 13 Ground

#### 2.3.2 AUDIO SUBSYSTEM

The MegaSTe® extends the present audio subsystem of the Atari ST® computer. It mixes the output of the existing ST programmable sound generator (PSG) with a DMA-driven dual channel digital to analog subsystem. The MegaSTe® combines these two sources and sends the resulting audio through the audio output pin of the monitor connector. In addition, the audio output can be connected to an external stereo amplifier for high-fidelity sound.

### 2.3.2.1 PROGRAMMABLE SOUND GENERATOR U305 PG. 3, U608 PG. 6

The programmable sound generator (U305) produces music synthesis, sound effects, and audio feedback. With an applied clock of 2 MHz, the PSG is capable of providing frequencies from 30 Hz to 112 kHz. The PSG has the ability to perform using three separate voice channels. The three sound channel outputs are mixed together and sent to the LMC1992 volume and tone control chip (U608).

#### 2.3.2.2 DMA SOUND

Sound in the form of digitized samples is stored in the system memory. These samples are fetched from dual purpose memory during horizontal blanking cycles and provided to a Digital to Analog Converter (DAC) at a constant sample frequency specified by the user. The output of the DAC is then low pass filtered to a frequency equal to forty percent of the sample frequency by a four pole switched capacitor low pass filter. The signal is further filtered by a two pole fixed frequency (15 kHz) low pass filter and sent to the LMC1992 Volume and Tone Control chip. The signal is then made available to two RCA type jacks at the back of the computer as well as the audio output pin of the monitor connector.

### 2.4 I/O SUBSYSTEMS

### 2.4.1 FLOPPY DISK INTERFACE U405 PG. 4

The floppy disk subsystem is designed around the Floppy Disk Controller supporting up to two daisy-chained disk drives. One internal and one external drive can be connected to the system. The subsystem interfaces to the RAM through the ACSI DMA controller. Commands and arguments are sent to the FDC by first writing to the DMA Mode Control Register to select the desired FDC register and then writing the data bytes. The standard drive for the system is a 720 Kbyte (capacity after formatting) 3 1/2-inch floppy disk. The internal drive cabling supports the Disk Change Line signal from the floppy drive and is read when the drive is selected, and is asserted when power is applied or a diskette is removed from the drive. The signal can be cleared by issuing a step command to the drive. Two clock speeds are provided to support both low and high density floppy drives. The decode for the register that hold the selection id done by PAL UA02 (Pg. 11). The signal is sent to PAL U407 (Pg. 4) where the proper clock is sent to the floppy disk controller.

#### 2.4.1.1 FLOPPY PORT PINOUT

<u>Pin</u> Function

- Read Data

Side 0 Select

- 3 Logic Ground

- 4 Index Pulse

- 5 Drive 0 Select

- 6 Drive 1 Select

- 7 Logic Ground

- 8 Motor On

- 9 Direction In

- 10 Step

- 11 Write Data

- 12 Write Gate

- 13 Track 00

- 14 Write Protect

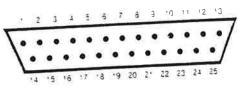

#### 2.4.1.2 INTERNAL FLOPPY DISK DRIVE CONNECTOR PINOUT

| <u>Pin</u> | <b>Function</b> |           |

|------------|-----------------|-----------|

| 1-33 Odd   | Ground          | ***       |

| 2          | FDDS            | 34 • • 33 |

| 4          | No Connect      | 32 • • 31 |

| 6          | No Connect      | 30 🔴 🕚 29 |

| 8 *3       | Index           | 28 💿 🕚 27 |

| 10         | Drive 0 Select  | 26 • 25   |

| 12         | Drive 1 Select  | 24 • 23   |

| 14         | No Connect      | 22 • 21   |

| 16         | Motor On        |           |

| 18         | Direction In    | 16 15     |

| 20         |                 | 14 13     |

| 22         | Step            | 12 0 11   |

| 24         | Write Data      | 10 0 9    |

|            | Write Gate      | 8 0 7     |

| 26         | Track 00        | 6 🔴 🌒 5   |

| 28         | Write Protect   | 4 🜒 🜒 3   |

| 30         | Read Data       | 2 🔴 🌒 1   |

| 32         | Side 0 Select   |           |

| 34         | No Connect      |           |

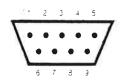

### 2.4.2 HIGH SPEED SERIAL PORTS SCC UA04 PG 11

The MegaSTe® contains an 85C30 Serial Communications Controller (SCC) that provides a dual channel, multi-protocol device that provides two serial ports. Port A can be used as either a network port or a standard slow speed RS232C serial port. The input/output of port A is routed to the appropriate connector, either an 8-pin mini-DIN or DB-9P, by setting a bit in a register (user application or Operating System). The output pins on the unselected port remain inactive

Port B is configured to be a low speed standard RS232C serial port that can be used for connecting a modem or local mainframe. The input/output of Port B is connected to a DB-9P connector and modem control signals are derived directly from the 85C30 Port B control lines. Port B can also operate with split transmit and receive baud rates.

The PCLK input to the SCC is rated at 8 MHz. The RTXCA and RTXCB input is provided with a 1.672 MHz clock. The TRXCA input comes from the LAN connector, and the TRXCB input is rated at 2.4576 MHz. Control signals are sent to the SCC by PAL UA03 (Pg. 11).

### 2.4.2.1 SCC RS-232 PINOUTS

#### Port A

#### <u>Pin</u> Function

- 1 Carrier Detect (In)

- 2 Receive Data (In)

- 3 Transmit Data (Out)

- 4 Data Terminal Ready (Out)

- 5 Ground

- 6 Data Set Ready (In)

- 7 Request to Send (Out)

- 8 Clear to Send (In)

- 9 No Connect

Port B

### Pin Function

- 1 Carrier Detect (In)

- 2 Receive Data (In)

- 3 Transmit Data (Out)

- 4 Data Terminal Ready (Out)

- 5 Ground

- 6 Data Set Ready (In)

- 7 Request to Send (Out)

- 8 Clear to Send (In)

- 9 No Connect

6

ω

σ

### 2.4.2.2 SCC LAN CONNECTOR PINOUT

Port A LAN Connector

#### Pin Function

- 1 Output Handshake (DTR, RS423)

- 2 Input Handshake (TRXCA external clock)

- 3 Transmit Data-

- 4 Ground

- 5 Receive Data-

- 6 Transmit Data+

- 7 (Reserved)

- 8 Receive Data+

### 2.4.3 MFP SERIAL PORT PG. 3

The 68901 MFP also provides a slow speed RS232C serial port to the system. The baud rate clock for the MFP serial port transmitter and receiver is derived from the timer D output of the MFP. Given the MFP's 2.4576 MHz clock, baud rates up to 19.2Kbaud can be supported. The MFP serial port is connected to a DB-9P connector and contains a complete complement of modem control lines, (excluding Data Set Ready, pin 6).

#### 2.4.3.1 MFP SERIAL PORT PINOUT

#### <u>Pin</u> <u>Function</u>

- 1 Carrier Detect (In)

- 2 Receive Data (In)

- 3 Transmit Data (Out)

- 4 Data Terminal Ready (Out)

- 5 Ground

- 6 No Connect

- 7 Request to Send (Out)

- 8 Clear to Send (In)

- 9 Ring Indicator (In)

ശ ß **m**

#### 2.4.4 PARALLEL INTERFACE U305 PG. 3

The parallel interface is implemented through the programmable sound generator chip. It is a subset of the Centronics® standard and is output to a DB25 connector. The Centronics STROBE signal is generated from the PSG bit. The Centronics BUSY signal is connected to one of the parallel input lines of the MFP (U404) to permit interrupt driven printing. Eight bits of read/write data are handled through I/O port B on the PSG at a typical transfer rate exceeding 4 Kbytes per second.

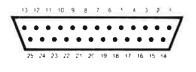

#### 2.4.4.1 PARALLEL PORT PINOUT

| <b>n</b> • | <b>T 1</b> |

|------------|------------|

| Pin        | Function   |

|            |            |

|            |            |

|            |            |

| 1     | STROBE        | -0           |                |

|-------|---------------|--------------|----------------|

| 2     | Data 0        | ~ •          | 14             |

| 3     | Data 1        |              | 15             |

| 4     | Data 2        | - • °        | 19 18 17 16 15 |

| 5     | Data 3        | <b>ب</b>     | 1              |

| 6     | Data 4        | <b>ه</b> ۵   | 18             |

| 7     | Data 5        | ~ • .        |                |

| 8     | Data 6        | ∞ •          | 21 20          |

| 9     | Data 7        | л <b>е с</b> |                |

| 10    | Not Connected | 0            | 24 23 22       |

| 11    | BUSY          | = • .        | 12             |

| 12-17 | Not Connected | - 12         |                |

| 18-25 | Ground        | 200          | 55             |

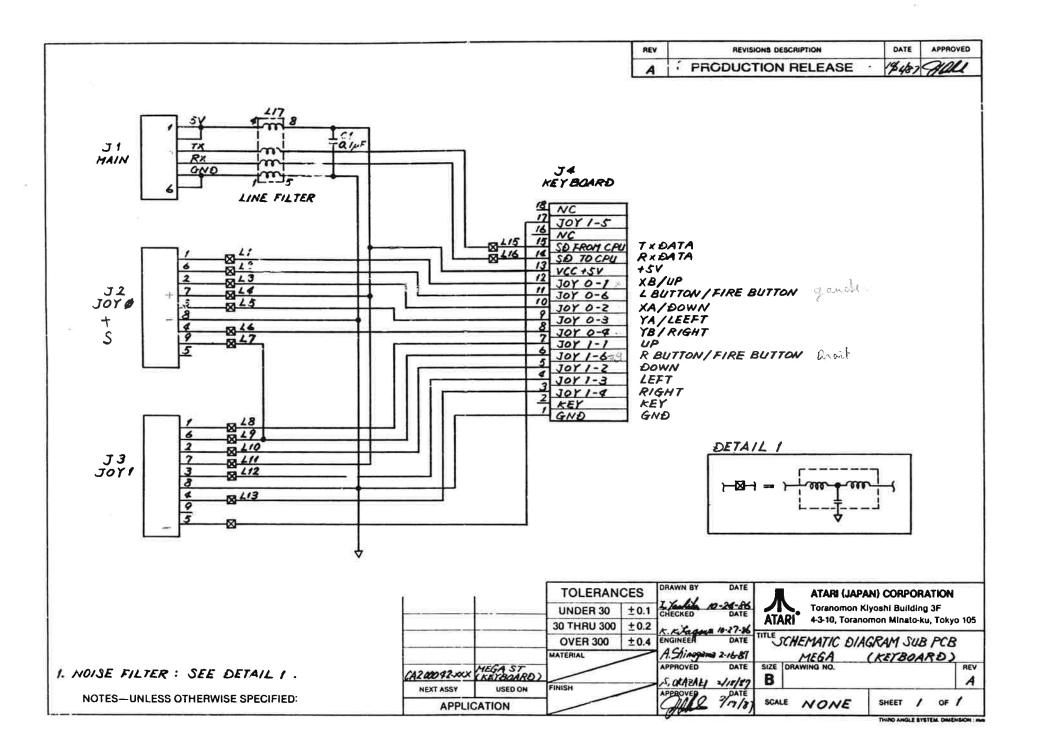

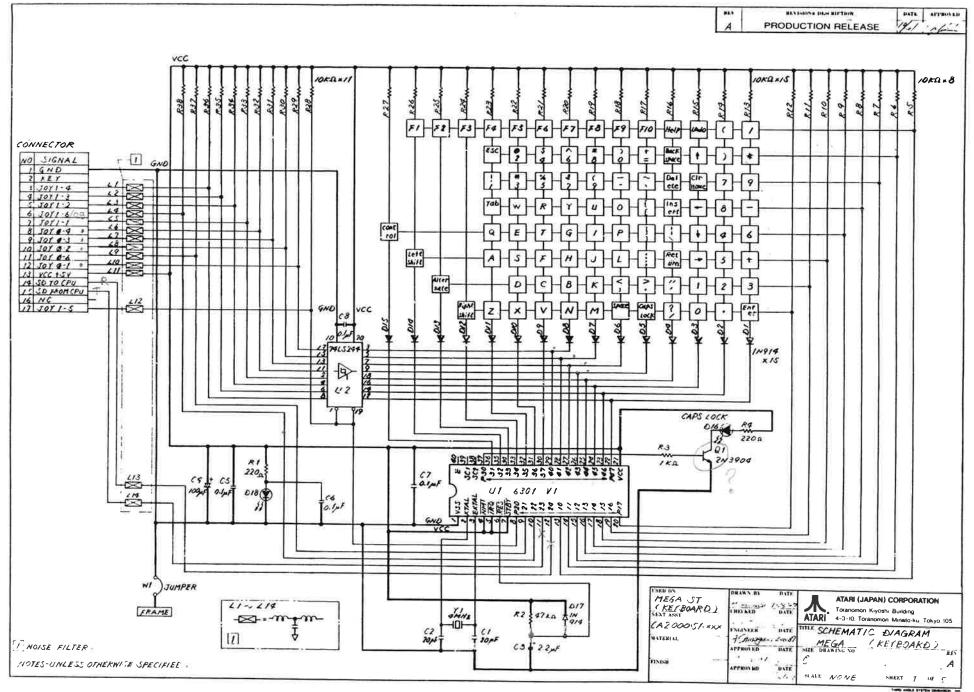

#### 2.4.5 KEYBOARD INTERFACE

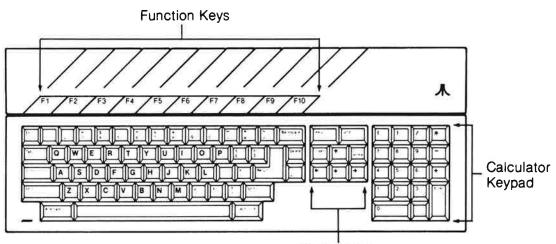

The keyboard transmits encoded make/break key scan codes (with two key rollover), mouse/trackball data, joystick data, and time-of-day. The keyboard receives commands and sends data via bidirectional communication implemented with an MC6850 Asynchronous Communications Interface Adapter (ACIA) and located in the keyboard. The data transfer rate is 7812.5 bits per second. The keyboard interfaces through a 6-pin telephone style jack.

#### 2.4.5.1 KEYBOARD CONNECTOR PINOUT

| <u>Pin</u> | Function |   |   |   |   |   |   |

|------------|----------|---|---|---|---|---|---|

| 1          | +5V      | L | 1 | E | 1 | T |   |

| 2          | +5V      |   | 2 |   |   |   |   |

| 3          | Transmit | 1 | 2 | S | 4 | 3 | D |

| 4          | Receive  |   | - |   |   | F |   |

| 5          | Ground   |   | L | _ | _ |   |   |

| 6          | Ground   |   |   |   |   |   |   |

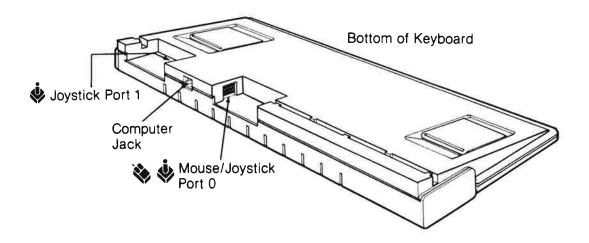

#### 2.4.6 MOUSE AND JOYSTICK INTERFACE

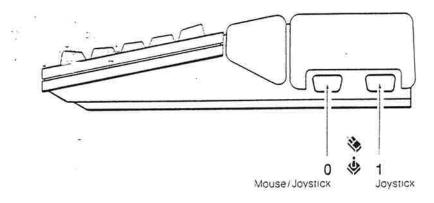

The Atari two-button mouse is a mechanical, opto-mechanical, or optical mouse with the minimal performance characteristics of 100 counts/inch, maximum velocity of 10 inches per second, and maximum pulse phase error of 50 %. The joystick is a four direction switch-type joystick with one fire button. The mouse and joystick are connected via two DB-9P connectors located on either side of the keyboard. A mouse or joystick can be connected on the right side of the keyboard. The connector on the left side of the keyboard is for joystick only.

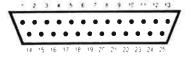

#### 2.4.6.1 MOUSE/JOYSTICK CONNECTOR PINOUT

<u>Pin</u> Function

| - |       |

|---|-------|

| 1 |       |

|   | UD XK |

|   |       |

- 2 Down XA

- 3 Left YA

- 4 Right YB

- 5 Not Connected

- 6 Fire/Left Button

- 7. +5VDC

- 8 Ground

- 9 JOY1/Fire Right Button

6 8 σ

-

#### 2.4.6.2 JOYSTICK CONNECTOR PINOUT

#### Pin Function

| 1 | Up                 |           | _         |   | 0  |

|---|--------------------|-----------|-----------|---|----|

| 2 | Up<br>Down         |           |           |   | w  |

| 3 | Left               |           | 2         | • |    |

| 4 | Right              |           | 3         | • | 7  |

| 5 | Right<br>Reserved  |           | 1157 - AL | • | 8  |

| 6 | <b>Fire Button</b> |           | 4         | • | 6  |

| 7 | +5VDC              |           | 2         | • | 0. |

| 8 | Ground             |           |           |   |    |

| 9 | Not Connected      | 545<br>10 |           |   |    |

#### 2.4.7 HARD DISK INTERFACE

Optional hard disks can be added to the system. The hard disk interfaces through the ACSI bus via a SCSI paddle board which plugs into the motherboard. The controller sends commands and data to the hard disk by way of the ACSI (Atari Computer System Interface) bus. All transfers to the hard disk are via DMA and the SCSI paddle board. DMA transfers are controlled by the SCSI paddle board via the HDRQ signal.

To access the SCSI paddle board the HDCS (Hard Disk Chip Select) signal is driven low and the CA1 signal to be asserted. The DMA support chip must respond with ACK low to acknowledge that data is on the bus or has been read from the bus. The Memory Controller internal to the GSTMCU then works with the DMA controller to write or read data from or into memory. Transfers can take place at up to 1 Mbyte per second.

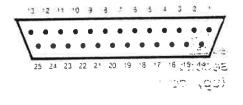

#### 2.4.7.1 EXTERNAL HARD DISK PINOUT (ACSI)

#### Pin Function

| 1  | Data 0            |

|----|-------------------|

| 2  | Data 1            |

| 3  | Data 2            |

| 4  | Data 3            |

| 5  | Data 4            |

| 6  | Data 5            |

| 7  | Data 6            |

| 8  | Data 7            |

| 9  | Chip Select       |

| 10 | Interrupt Request |

| 11 | Ground            |

| 12 | Reset             |

| 13 | Ground            |

| 14 | Acknowledge       |

| 15 | Ground            |

| 16 | A1                |

| 17 | Ground            |

| 18 | Read/Write        |

| 19 | Data Request      |

|    | •                 |

M 16 15 14 13 4 ഹ g ΩC 3 **O** σ

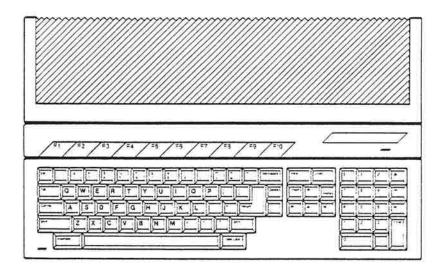

#### 2.4.8 ROM CARTRIDGE

The MegaSTe® contains a ROM cartridge port that is fully compatible with the Atari ST® cartridges. The cartridge is physically connected through a 40-pin edge connector located on the left side of the case. ROM cartridges are mapped to a 128 Kbyte area starting at address FA0000 and extending to FB8FFF.

### 2.4.9 MUSICAL INSTRUMENT DIGITAL INTERFACE (MIDI)

The MegaSTe® is also equipped with a Musical Instrument Digital Interface (MIDI) which provides high speed serial communication of musical data to and from sophisticated synthesizer devices. The Musical Instrument Digital Interface (MIDI) allows the integration of the MegaSTe® with music synthesizers, sequencers, drum boxes, and other devices possessing MIDI interfaces. High speed (31.25 Kbaud) asynchronous current loop serial communication of keyboard and program information is provided by two ports, MIDI OUT and MIDI IN (MIDI OUT also supports the optional MIDI THRU port).

MIDI specifies that data consist of eight data bits, one start bit, and one stop bit. The MIDI OUT and MIDI IN connector pinouts are as follows:

MIDI OUT

<u>Pin</u> Function

- 1 THRU Transmit Data

- 2 Shield Ground

- 3 THRU Loop Return

- 4 OUT Transmit Data

- 5 OUT Loop Return

MIDI IN

<u>Pin</u> Function

- 1 Not Connected

- 2 Not Connected

- 3 Not Connected

- 4 IN Receive Data

- 5 IN Loop Return

#### 2.4.10 VME BUS PG. 9, 10

The VME bus is provided for system expansion. The bus is composed of 23 address lines and 16 data lines. Control for the bus is provided by PAL U903 (Pg. 9) and U904 (Pg. 9). External interrupt requests to the VME bus are handled by the SCU IC U801 (Pg. 8).

The VME bus in the MegaSTe® complies with the Vita C.1 specification. It supports A24/D16 or A16/D16 slave cards only.

#### 2.5 SYSTEM STARTUP

After a RESET (power-up or reset button) the 68000 will start executing at the address pointed to by locations 4-7, which is ROM (GSTMCU maps the first 8 bytes of ROM at E00000-7 into addresses 0-7). Location 000004 points to the start of the operating system code in ROM. The following sequence is then executed:

- 1. Perform a reset instruction (outputs a reset pulse to reset hardware registers).

- 2. Read the longword at cartridge address FA0000. If the data read is a "magic number", execute from the cartridge (ROM cartridge instructions take over here).

- 3. If not, continue.

- 4. Check for a warm start (see if RAM locations contain valid data), initialize the memory controller.

- 5. Initialize the PSG chip, deselect disk drives.

- 6. Initialize color palettes and set screen address.

- 7. If not a warm start, zero memory.

- 8. Set up operating system variables in RAM.

- 9. Set up exception vectors.

- 10. Initialize MFP.

- 11. Set screen resolution.

- 12. Attempt to boot floppy; attempt to boot hard disk; run program if succeeded.

- 13. If no boot disk, the 256K boot ROM will bring up the desktop.

#### 2.6 SYSTEM ERRORS

The 68000 has a feature called exception processing, which takes place when an interrupt or bus error is indicated by external logic, when the CPU detects an error internally, or when certain types of instructions are executed. An exception will cause the CPU to fetch a vector (address to a routine) from RAM and start processing at the routine pointed to by the vector. Exception vectors are initialized by the operating system. Those exceptions which do not have legitimate occurrences (interrupts being legitimate) have vectors pointing to a general purpose routine which will display some number of bombs showing on the screen. The number of bombs equals the number of the exception which occurred.

System errors may or may not be recoverable. Errors in loading files from disk may cause the system to crash, necessitating a reset. Verify the diskette and disk drive before attempting to repair the computer.

### 2.6.1 NUMBER OF BOMBS AND MEANING

| Bombs    | Meaning                                                                                                                                                                                                           |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2        | Bus Error. GSTMCU (U501) asserted bus error. This condition<br>can be due to faulty MFP (U306), RAM (U701, U702, U703,<br>U704), ROM (U206, U207), PSG (U305), or a short/open on<br>the PCBA address/data lines. |

| 3        | Address Error. Processor attempted to access word or long word sized data on an odd address.                                                                                                                      |

| 4        | Illegal Instruction. Processor fetched an instruction from ROM or RAM which was not a legal instruction.                                                                                                          |

| 5        | Zero Divide. Processor was asked to perform a division by zero.                                                                                                                                                   |

| 6        | Chk Instruction. This is a legal instruction, if software uses this, it must install a handler.                                                                                                                   |

| 7        | Trapy Instruction. See Chk instruction.                                                                                                                                                                           |

| 8        | Privilege Violation. CPU was in user mode, tried to execute a supervisor instruction.                                                                                                                             |

| <b>9</b> | Trace. If trace bit is set in the status register, the CPU will execute this exception after every instruction. Used to debug software.                                                                           |

| 10       | Line 1010 Emulator. CPU read pattern 1010 as an instruction.<br>Provided to allow user to emulate his own instructions.                                                                                           |

| 11       | Line 1111 Emulator. See Line 1010 Emulator.                                                                                                                                                                       |

| 12-23    | Unassigned, should be no occurrence.                                                                                                                                                                              |

| 24       | Spurious Interrupt. Bus error during interrupt processing.                                                                                                                                                        |

| 25-31    | Autovector Interrupt. Even numbered vectors are used, others should have no occurrence.                                                                                                                           |

| Bombs  | Meaning                                                                   |

|--------|---------------------------------------------------------------------------|

| 32-63  | TRAP Instruction. CPU read instruction which forced exception processing. |

| 64-79  | MFP interrupts.                                                           |

| 80-255 | User interrupts.                                                          |

đ

### 2.7 ATARI MEGASTE BLOCK DIAGRAM

27

### SECTION THREE

### TESTING ---

### **3.1 OVERVIEW**

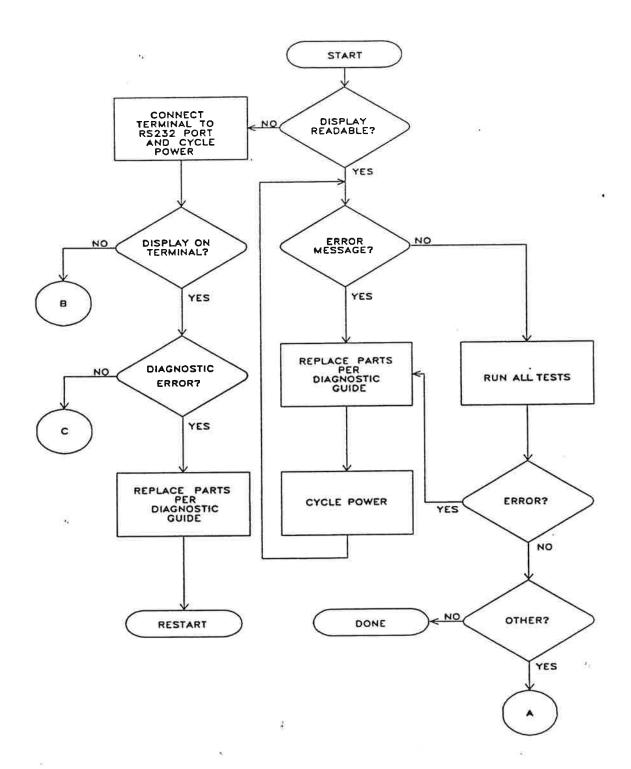

This section pertains to the test equipment, diagnostic software, and test procedures used to verify correct operation and repair of the MegaSTe® computer. The diagnostic cartridge should be used if possible. If the unit gives no display or RS232 output when running the cartridge, see "Troubleshooting a Dead Unit" below.

Since the level of complexity in the MegaSTe® system is high, it should not be expected that this document can cover all possible problems or pinpoint the causes; rather, the intent here is to give a systematic approach which a technician can use to narrow down a problem to its most likely source. Experience in troubleshooting computer systems is assumed. Knowledge of the 68000 processor is helpful.

Economics will be an important consideration; due to the low cost of the MegaSTe® computer, little time can be justified in troubleshooting down to the component level when it may be cheaper to replace the functional subassembly. Many of the more expensive (and critical) components are socketed, making verification and replacement faster.

### **3.2 TEST EQUIPMENT**

The following equipment will be needed to test the MegaSTe® computer:

- Atari SC1224 RGB Monitor

- Atari SM124 Monochrome Monitor

- SF314 External Floppy Disk Drive

- MegaSTe® Port Test Fixture

- RS232 Loop-Back Connector (3)

- MIDI Loop-Back Cable

- MegaSTe® Test Diagnostic Cartridge Rev. 1.3

- Blank Double Sided 3 1/2-inch Diskettes (2)

- LAN Loopback Connector

$\tilde{t} \geq 0$

14

Optional (for troubleshooting):

- RS232 terminal (or STe® with VT52 emulator)

- RS232 Null Modem Cable

In addition, the following items may be required to troubleshoot and repair the unit:

- 2 Channel 100MHz Oscilloscope

- Small Hand Tools

- Spare Parts

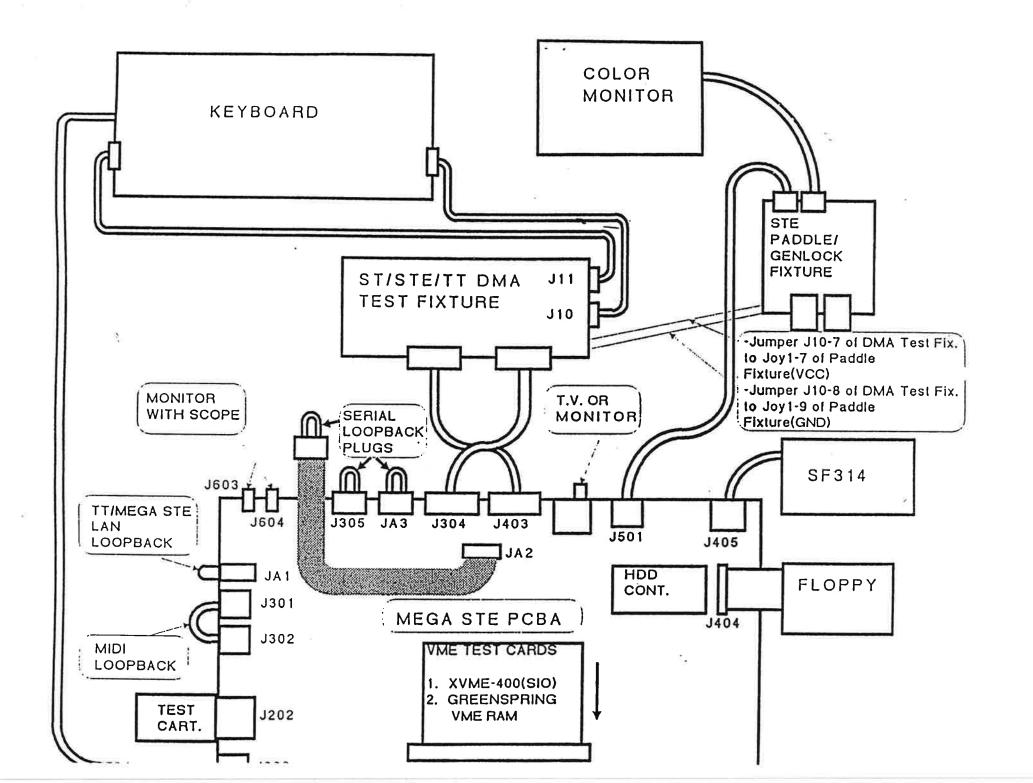

#### **3.3 TEST CONFIGURATION**

With the power switch off, install the Diagnostic Cartridge with the label facing up.

# IMPORTANT--if the cartridge does not have the plastic enclosure, BE SURE THE CARTRIDGE IS INSTALLED WITH THE CHIPS FACING DOWN).

Connect cables from the STe® test fixture into the hard disk port, parallel port, and joystick/mouse ports. The joystick cables should be plugged in so that, if the fixture ports were directly facing the computer ports, the cables would not be crossed. Plug the MIDI loopback cable and LAN loopback connector into their ports. Plug the color monitor into the monitor output (a monochrome can be used instead).

# NOTE: THE RS232 LOOPBACK CONNECTORS SHOULD ONLY BE PLUGGED IN AFTER THE MENU IS DISPLAYED.

Make sure the switch on the STe® test fixture is in the position marked INT, otherwise the program will not proceed past the initialization. The other position is GENLOCK. The GENLOCK test is discussed later in section 3.4.4.

Power on the unit. Some tests will be run automatically; in a few seconds the menu screen should appear. If the screen appears, skip down to "MegaSTe® Diagnostic Cartridge", below. If not, read next section "Troubleshooting a Dead Unit".

$\mathcal{X}^{(n)}$

#### **3.4 TROUBLESHOOTING A DEAD UNIT**

In the event that the system is correctly configured and powered on and no display appears, this is the procedure to use for determining the problem. This assumes elementary steps have been taken, such as checking the power LED to verify the unit is powered on and making sure the monitor is working. If the LED in the forward left corner is not illuminated, check the power supply voltages first. If voltages require adjusting, perform the adjustments. If the power supply is defective, replace the supply, then if the LED is still not illuminated, check to see if it is defective.

- 1. Connect a dumb terminal to the RS232 port of the unit under test (U.U.T.). You can use an STe® running the VT52 terminal emulator program. Please see the owner's manual for setting up VT52. The cable should connect pin 3 (serial out) of the U.U.T to pin 2 (serial in) of the terminal, and vice versa. Connect pin 7 (ground) to pin 7. The terminal should be set up for 9600 bps, 8 bits of data, 1 stop bit, no parity (this is the default condition for the VT52 emulator).

- 2. Insert the Diagnostic Cartridge into the U.U.T., and power on the unit. If the Diagnostic Cartridge messages appear on the display of the terminal, use the diagnostic to troubleshoot the computer. If not, the computer will have to be disassembled to troubleshoot. Refer to "MegaSTe® Diagnostic Cartridge" below for information on using the cartridge. If no activity is seen on the RS232 port or display, continue with (2) below.

- 3. Disassemble the computer so that the printed circuit board is exposed (see Section 4, Disassembly). Power up the computer. Using an oscilloscope, verify the 8 MHz clock to the 68000 CPU (pin 15). Replace oscillator if necessary. Then check pin 17 (HALT) of the 68000 CPU. It should be a TTL high. If so, go on to 5 below. If not, the CPU is halted. The reasons may be: (1) bad reset circuit, (2) double bus error, 3) bad CPU.

- 4... Check (1) by observing signal on input of the two inverters on the HALT line. Check (2) by observing pin 22 of the CPU (BERR) as the unit is powered on. It should be high always. If there are logic low pulses, some component is malfunctioning and GSTMCU is generating the error. Verify the clocks to GSTMCU and replace these components to verify them (if socketed).

- 5. If still failing, the CPU is unable to read ROM or there is a component which is not responding to a read or write by the CPU, probably the MFP 68901 or DMA Controller. The MFP should respond to an MFPCS with DTACK. The DMA chip should respond to FCS by asserting RDY. There is no way to check for a bad 68000 other than by elimination of the other two possibilities, although a hot CPU (too hot to touch for more than a second) strongly indicates a bad CPU.

- 6. If the CPU is not halted, it should be reading instructions from ROM cartridge, if installed, and data and address lines will be toggling. (If not, replace CPU.) At this point, there is the possibility that both the video and RS232 subsystems are failing. Verify the output of the MFP chip (pin 9) while powering on the unit with the cartridge installed. If data is being sent, trace it through the 1488 driver. Note that + and 12v. is required for RS232. If all looks good, here may be something wrong with the connection to the terminal.

- 7. Verify also the output of the Video Shifter. If using an RGB monitor, check the outputs to the summing resistors for R, G, and B. Note that if BLANK is not going high, no picture will be possible. If using monochrome, check output pin 50. Also check the input to the MFP, pin 32, MONOMON-. Note that if the CPU does not read a low on this signal on power-up, it will cause RGB output on the Video Shifter.

- 8. If the Video Shifter is outputting a signal, but the picture is unreadable, there is probably a problem with screen RAM. The cartridge should be used to diagnose this problem, with the RS232 terminal as a display device.

### **3.4 MEGASTE® DIAGNOSTIC CARTRIDGE**

The MegaSTe® Diagnostic Cartridge is used to detect and isolate component failures in the MegaSTe® computers. This document refers to revision 1.3. Users of earlier versions should refer to the appropriate Troubleshooting Guide. This section gives a brief guide to use with a description of each test, error codes or pass/fail criteria, and recommendations on repair.

#### 3.4.1 POWER-UP

The diagnostic program performs several tests on power-up. In particular, the message "Testing MFP, GSTMCU timing, Video will appear, and the screen will appear scrambled for a few seconds before the menu is printed. The screen will turn red (dark background in monochrome) if an error occurs in the initial testing, with a message indicating the failure. The lowest 2 Kbytes of RAM is tested on power-up; if a location fails, the error will be printed to the RS232 device. It is assumed that if RAM is failing, the screen may not be readable and program execution will fail because there is no stack or system variables. The program will continue to test RAM and print errors, but no screen will be displayed (the screen may turn red). Repair RAM.

If the keyboard fails, it will be inactivated. The user must connect a terminal to the RS232 port. The diagnostic program looks for keystrokes from the RS232 device.

If the display is unreadable, the RS232 terminal should be used. All messages are printed to the RS232 port as well as the screen.

32

ł

11

# **3.4.2 POWER-UP INITIALIZATION ERRORS**

# INITIALIZATION (ERRORS OCCURRING BEFORE THE TITLE AND MENU APPEAR.)

- I1 RAM data line is stuck.

- I2 RAM disturbance. Location is altered by write to another location.

- I3 RAM addressing. Wrong location is being addressed.

- I4 MMU error. No DTACK after RAM access.

- I5 RAM sizing error. Uppermost address fails.

- I6 Bus Error handling failed. Bus Error occurred (on purpose), but caused a crash (e.g. system was unable to read the vector from RAM).

- I7 Bus Error not detected. GSTMCU not asserting Bus Error or the signal is not reaching the 68000.

- T0 MFP timers failed.

- T1 Vertical sync timing failed.

- T2 Horizontal sync timing failed.

- T3 Display Enable Interrupt failed.

- T4 Memory Controller video address counter failed.

- T5 PSG Bus test. PSG chip is causing a bus error by staying on the data bus too long.

- T6 Floppy Disk Controller Bus test. FDC chip is causing a bus error by staying on the data bus too long.

- K0 Stuck key

- K1 Keyboard controller is not responding.

- K2 Keyboard controller reports error.

## 3.4.3 TEST MENU

The normal screen will be dark blue with white letters. The test title and revision number are displayed at the top, with the amount of RAM and keyboard controller revision below, and a test menu below that. To select tests, the user types the keys corresponding to those tests, and then the RETURN key. After the operator selects a test, the program will not proceed until the key break is detected (when the operator releases the key).

This prevents false "stuck key" messages in the keyboard test. Many iterations of the test or tests chosen can be run by typing in the number of cycles just before typing RETURN. Typing a zero will cause the test sequence to run continuously. To stop a cycle before completion, hit the ESC key (there may be some delay in some tests before the test stops). As each cycle completes, the total numbers of cycles will be displayed on the screen. Several hidden key sequences are also provided.

#### MAIN MENU:

Mega-STe® Field Service Diagnostic Test Rev. 1.3 © 1991, Atari Corp. 4M RAM Keyboard revision 2 60 Hz O.S. Version 2.02 USA NTSC

R RAM Test M MIDI D DMA Port F Floppy Disk G short BLiT O O.S. ROMs K Keyboard S Serial Port T Timing I SCC L Real-Time Clock P Printer/Mouse/Joy Ports Y long BLiT V VME

Q Run All Unattended Tests (R,O,K,M,S,T,D,I,L,F,P,Y,V) Z Run Unattended Internal tests (R,O,K,G,T,V,L)

A Audio C Color H High resolution J Hard Disk Read/Write

E Examine/Modify memory B Set RS232 rate X Toggle video output--50/60 Hz ? Help

Enter Letter(s), and Return

#### HIDDEN KEY SEQUENCES:

<Shift> 1 System Clock 8 MHz cache off <Shift> 2 System Clock 16 MHz cache off <Shift> 3 System Clock 16 MHz cache on <Shift> 5 8 MHz floppy clock set <Shift> 6 16 MHz floppy clock set (1.44 Meg Drive)

<Shift> 7 Software Date

The RAM size, keyboard revision, O.S. version, country (or language), and television standard (PAL or NTSC) are shown.

The 'Q' selection sequences through all the tests except for Audio, Color, High resolution monitor, and Hard Disk Read/Write. The 'Z' selection sequences through RAM, ROM, Keyboard, short BLiT, Timing, VME, and Real-Time Clock. Selection 'E' enables the operator to examine or modify RAM or hardware registers. 'B' enables the operator to change the baud rate on the RS232 port. Pressing the up arrow increases it, pressing the down arrow decreases it.

For example T M2 L3 V0 <ENTER> would result in the Timing test being run once, MIDI test twicw, Real-Time Clock test three times, and VME indefinitely or until the <ESC> key is pressed.

After a test or series of tests completes, the pass/fail status and error report, if any, will be displayed. When the selected test(s) have passed the screen will turn green accompanied by a short beep. If the selected test(s) fails the screen will turn red accompanied by an audible tone which oscillates. This allows the user to perform other troubleshooting functions while the running diagnostics without having to look directly at the screen for an indication of a Pass or Fail status. Press the space bar to return to the menu.

If multiple tests are selected, the sequence can be halted before completion by pressing the ESC key. At the completion of the current test, the sequence will halt, with the options of either continuing or returning to the menu. In some cases there will be a considerable delay before the current test completes and the keystroke is detected.

## **3.4.4 SUMMARY OF TESTS**

#### **3.4.4.1 GENLOCK**

The GENLOCK switch position allows the system to synchronize the MegaSTe® video with an external source. The system clock is also phase-locked to the input sync signal. To do this pin three of the monitor connector is grounded, and the external clock is sent to the system on pin 4.

The GENLOCK test can be run using the INT/GENLOCK switch on the MegaSTe® port test fixture. The GENLOCK test is run twice. Toggling the switch to the GENLOCK position on the STe® test fixture should switch between the normal menu and no menu. With no menu a "sweeping" cycle should be heard. Reset the computer between each change of the INT/GENLOCK switch.

#### NOTE: RUN THIS TEST ONLY WITH A COLOR MONITOR.

#### 3.4.4.2 RAM TEST (R)

System RAM is tested in three stages: low 2 kbytes, middle (up to 64k), and from 64k to top. The test patterns used are: all ones, all zeros, a counting pattern (data=low word of the address), reverse counting pattern (data=complement of address low word). The counting pattern is copied from the top and bottom of a 32 Kbyte buffer into the current 32 Kbytes of video RAM, then shifts video RAM to a new area, verifies the pattern, and repeats the test, until the top of RAM is reached. Finally, addressing at 64k boundaries is checked by writing unique pattern in last 256 bytes of each 64k block. The cache RAM is also tested as well as a CAS1 test to detect opens and shorts on the CAS signal for the upper bank of memory.

If an error occurs, the display turns red accompanied by an oscillating tone and the error code is displayed, followed by the address, data written, data read, and the bits which did not agree.

For example: " R2 45603E W:603E R:613C bad bits: 1,8".

In units having more than one bank the address as well as the bit position must be used to find the correct SIMM. The following table gives a correspondence between the addresses and banks for various models:

# **ONE MEGABYTE MACHINES**

| Address        | <u>Bank</u> | <u>Bad Bit(s)</u> | <u>SIMM</u> |

|----------------|-------------|-------------------|-------------|

| 0-07FFFF       | bank 0      | 1-8               | U703        |

|                | bank 0      | 9-16              | U701        |

| 0080000-0FFFFF | bank 1      | 1-8               | U704        |

|                | bank 1      | 9-16              | U702        |

# TWO AND FOUR MEGABYTE MACHINES

| Address       | <u>Bank</u> | Bad Bit(s) | <u>SIMM</u> |

|---------------|-------------|------------|-------------|

| 0-1FFFFF      | bank 0      | 1-8        | U703        |

|               | bank 0      | 9-16       | U701        |

| 200000-3FFFFF | bank 1      | 1-8        | U704        |

|               | bank 1      | 9-16       | U702        |

A bank is 16 bits wide and consists of two 1Mbit X 8 SIMMS.

## **RAM ERROR CODES**

Except where noted, repair by replacing the SIMM corresponding to the indicated bit(s).

| RO        | Error in low memory, possibly affecting program execution.              |

|-----------|-------------------------------------------------------------------------|

| R1        | Error in SIMM.                                                          |

| R2        | Address error. Bad SIMM or memory controller. Address line not working. |

| R3        | Address error at 64k boundary.                                          |

| R4        | Error during video RAM test. Bad SIMM.                                  |

| Cache RAM | Error during cache RAM test. Bad cache RAM chip.                        |

37

#### 3.4.4.3 ROM TEST (O)

This test reads the configuration bytes of the operating system to determine the version, language/country, and TV standard (PAL or NTSC). All bytes from operating system ROMs are then read and the checksums are calculated and displayed. A CRC is then calculated for each EPROM.

The test fails if the CRC calculated does not match the CRC found in the last location in each EPROM (e.g. Version 2, French). Incorrect CRCs are indicated by the display turning red and an oscillating tone followed by a message. If an error is displayed, replace the corresponding ROM.

#### 3.4.4.4 COLOR TEST (C)

This test verifies the Video Shifter. Seven color bands are displayed: red, green, blue, cyan, magenta, yellow, and white. Each band consists of 8 levels of intensity. All 16 color palettes are represented, each palette is a vertical strip across the screen (strips should not be discernable, but each color should be a straight line across the screen). Because of the tight timing involved, keystroke interrupts will cause the display to jitter.

The operator should see that there are no gaps or missing scan lines in the display. If lines are missing, check the three outputs on the Video Shifter for that color, and verify the values of the resistors on the output. Too low a brightness setting on the monitor will cause the monitor not to distinguish between fine levels, making it appear there are only four levels being output.

The Video Shifter has four outputs for red (R0,R1,R2,R3), green (G0,G1,G2,G3) and blue (B0,B1,B2,B3). Each of these outputs is summed together by a resistor network to give 8 levels of intensity for each color, depending on which of the outputs are on. The values of the resistors give different weight to each output. The value of the resistor at R0 is twice that of R1, which is twice that of R2. (Note: some versions have these resistors inside the shifter.)

This allows us to get 8 equal steps on the summed outputs. For example, R0 on and R1 and R2 off = 1/8, R0 off, R1 and R2 on = 7/8. This signal then passes through a transistor amplifier, and from there to the video monitor connector.

# NOTE: THIS RESISTOR NETWORK IS INCORPORATED INTO THE GATE ARRAY CHIP IN LATER VERSIONS.

#### SYMPTOMS AND FIXES:

- 1. Missing primary color. Check the output of the transistor amplifier. Q503 is blue, Q502 is green, Q501 is red. Look for a staircase pattern (eight levels of intensity). If the signal is there, trace forward to the video connector, if not, trace backward to the Video Shifter, until the faulty component is found.

- 2. Primary colors present, secondaries missing or incorrect. Replace the Video Shifter (U502).

- 3. Coarse change in intensity (not a smooth dark to light transition). Replace Video Shifter (U502) or look for a short on the output of one of the three color outputs for the appropriate color.

- 4. Specks or lines on the screen. This can be caused by bad RAM; if RAM has been tested and is good, replace the Video Shifter (U502).

- 5. Wavering display, horizontal lines not occurring in the same place every time. The processor may be getting extra interrupts (if the processor is required to handle additional interrupts, it will not have time to change all color registers during a horizontal scan time). Examine the MFP interrupt request (pin 32). There should be an interrupt every 126 microseconds (2 display lines) from Display Enable (pin 20). If additional interrupts occur, locate the source: the inputs at pins 22-29 should all be high. If no external (to the MFP) source for the interrupts is found, replace the MFP (U306). NOTE: if the keyboard is not connected, the input to the 6850 will be low, causing continual interrupts.

#### 3.4.4.5 KEYBOARD TEST (K)

Two types of test are run. The keyboard self-test is done first, and if this passes, a screen is displayed representing the keyboard. The operator presses keys and observes that the corresponding character on the screen changes (reverses background color). The key will also be displayed in the lower half of the screen. The mouse buttons and four directions are also shown on the screen. Connect the mouse and move in any direction and the arrow will flicker. Any key clicks while the mouse is moving indicates a short.

NOTE: it is possible, if pressing keys very rapidly, to leave the representation of the key on screen in a depressed state. This does not indicate a problem with the hardware.

The self-test checks communication between the CPU and the keyboard microcomputer, and checks RAM and ROM in the keyboard microcomputer, and scans the keyboard for stuck keys.

### **KEYBOARD ERROR CODES**

- K0 Stuck key. A key closure was detected while the keyboard self test was executing.

- K1 Keyboard not responding. A command was sent to the keyboard processor and no status was returned within the allowed time. The keyboard needs to be replaced or the communication channel through the 6850 (U304) is not functional.

- K2 Keyboard status error. The self test command was sent to the keyboard, on completion of the test, the keyboard sent an error status. Replace the keyboard.

### 3.4.4.6 MIDI TESTS (M)

This test sends data out the MIDI port, (data loops back through the cable) and reads from the input and verifies the data is correct. This also tests the interrupt from the 6850 through the MFP chip. The LED in the loopback cable will blink as data is sent (not all cables have the LED).

#### MIDI ERROR CODES

- --

| МО | Data not received. Trace the signal from the output of the 6850 (U303), through the drivers (U301), loopback cable, and receivers to the input of the 6850 (U303). Replace the defective component. |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M1 | Write/Read data mismatch. The data written was not the same as the data read. Replace 6850 (U303).                                                                                                  |

| M2 | Input frame error. Bad 6850 (U303) or bad driver (U301) or receiver causing noisy signal.                                                                                                           |

| М3 | Input parity error. Bad 6850 (U303) or bad driver (U301) or receiver causing noisy signal.                                                                                                          |

| M4 | Input data overrun. The 6850 received a byte before the previous byte was read. Probable bad 6850 (U303), also can be caused by the MFP (U306) not responding to the interrupt request.             |

#### **3.4.4.7 SERIAL PORT TESTS (S)**

## NOTE: DO NOT INSTALL THE RS232 LOOPBACK CONNECTORS UNTIL AFTER THE MAIN MENU IS DISPLAYED.

First the RS232 control lines are tested (which are tied together by the loopback connector), then the data loopback is tested. Data is checked transmitting/receiving using a polling method first, then using interrupts.

Data is transmitted at 300, 600, 1200...19200 bps. Data transmission is performed by the MFP and the 1488 and 1489 driver and receiver chips (U310, U311). Interrupts are a function of the MFP (U306). Control lines are output by the PSG chip (U305) and input on the MFP. Note that this test does not thoroughly test the drive capability of the port. If the test passes, but the unit fails in use, it is likely that the 1488 (U311) or 1489 (U310) chips are bad.

## SERIAL PORT ERROR CODES

#### Data transmission error:

| S0 | Data not received. Check signal path: MFP (U306) pin 9 to 1488 (U311) pin 5 to J305 pin 3 to J305 pin 2 to 1489 (U310) pin 1 to MFP (U306) pin 10. |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------|

| S1 | Data mismatch. Data read was not what was sent. Check integrity of the signal. May be bad driver (U311), receiver (U310), or MFP (U306).           |

| S2 | Input frame error. Incorrect time between start and stop bits.<br>Probable MFP failure (U306).                                                     |

| S3 | Input parity error. Input data had incorrect parity. Probable MFP failure (U306).                                                                  |

| S4 | Input data overrun. A byte was received before the CPU read<br>the previous byte. MFP failure (U306) or, less likely,<br>GSTMCU (U501) failure.    |

| S5 | No IRQ. CPU did not detect an interrupt by the MFP. MFP (U306) or GSTMCU (U501) failure.                                                           |

| S6 | Transmit error. MFP (U306) transmitter failed.                                                                                                     |

|    |                                                                                                                                                    |

## SERIAL PORT ERROR CODES (CONTINUED)

| S7        | Transmit error interrupt. An error condition was created intentionally to cause an interrupt, and the MFP did not respond. |

|-----------|----------------------------------------------------------------------------------------------------------------------------|

| <b>S8</b> | Receive error interrupt. An error condition was created intentionally to cause an interrupt, and the MFP did not respond.  |

| S9        | RI/DTR connection. Signal sent at DTR is not detected at RI.                                                               |

| SA        | DCD/DTR connection. Signal sent at DTR is not detected at DCD.                                                             |

| SB        | RTS/CTS connection. Signal sent at RTS is not detected at CTS.                                                             |

| SC        | RS232 input shorted to output. The input and outputs of the MFP serial port are shorted together.                          |

## 3.4.4.8 SCC TEST (I)

The SCC diagnostic tests the SCC chip for several functions. Internal loopback polled (asynch), break (test ext loopback), external loopback polled (asynch), modem control lines, and external loopback interrupt (asynch). Ports A and B are tested in RS232 mode, and the LAN at port A is also tested.

## SCC ERROR CODES

## **PORT A ERRORS:**

SCC A internal loopback: Transmitter time-out Transmitter failed.

| SCC A internal loopback: Receiver time-out | Receiver failed.                                           |

|--------------------------------------------|------------------------------------------------------------|

| SCC A internal loopback: Overrun           | A byte was received before the CPU read the previous byte. |

| SCC A internal loopback: Framing error     | Incorrect time between start and stop bits.                |

| SCC A internal loopback: Parity error      | Input data had incorrect parity.                           |

| SCC A internal loopback: Data compare      | Data read was not what was sent.                           |

Port A has no loopback connector

LAN has no loopback connector

The loopback connector is not installed on Port A.

The loopback connector is not installed on the LAN Port.

#### LAN ERROR: DCD IS ACTIVE WITHOUT RTS ON

The Carrier detect signal is active without a request to send.

#### LAN ERROR: RTS IS ACTIVE BUT DCD IS NOT RESPONDING

The request to send signal is on but no carrier is active.

Port A async mode: Transmitter time-out Port A async mode: Receiver time-out Port A async mode: Overrun

Port A async mode: Framing error

Port A async mode: Parity error

Port A async mode: Data compare

Port A modem control error: DTR-DCD

Port A modem control error: DTR-DSR

Port A modem control error: RTS-CTS

Receiver failed.

Transmitter failed.

A byte was received before the CPU read the previous byte.

Incorrect time between start and stop bits.

Input data had incorrect parity.

Data read was not what was sent.

Signal sent at DTR is not detected at DCD.

Signal sent at DTR is not detected at DSR.

Signal sent at RTS is not detected at CTS.

#### **PORT B ERRORS:**

SCC B internal loopback: Transmitter time-out Transmitter failed.

SCC B internal loopback: Receiver time-out Receiver failed.

SCC B internal loopback: Overrun

SCC B internal loopback: Framing error

SCC B internal loopback: Parity error SCC B internal loopback: Data compare Port B has no loopback connector

Port B async mode: Transmitter time-out

Port B async mode: Receiver time-out

Port B async mode: Overrun

Port B async mode: Framing error

Port B async mode: Parity error

Port B async mode: Data compare

Port B modem control error: DTR-DCD

Port B modem control error: DTR-DSR

Port B modem control error: RTS-CTS

## SCC INTERRUPT ERRORS:

SCC interrupt error: Transmitter time-out SCC interrupt error: Receiver time-out SCC interrupt error: Overrun A byte was received before the CPU read the previous byte.

Incorrect time between start and stop bits.

Input data had incorrect parity.

Data read was not what was sent.

The loopback connector is not installed on Port B.

Transmitter failed.

Receiver failed.

A byte was received before the CPU read the previous byte.

Incorrect time between start and stop bits.

Input data had incorrect parity.

Data read was not what was sent.

Signal sent at DTR is not detected at DCD.

Signal sent at DTR is not detected at DSR.

Signal sent at RTS is not detected at CTS.

Transmitter failed.

Receiver failed.

A byte was received before the CPU read the previous byte.

| SCC interrupt error: Framing error | Incorrect time between start and stop bits.              |

|------------------------------------|----------------------------------------------------------|

| SCC interrupt error: Parity error  | Input data had incorrect parity.                         |

| SCC interrupt error: Data compare  | Data read was not what was sent.                         |

| No Tx interrupt                    | A transmit command was issued but no interrupt occurred. |

| No Rx interrupt                    | A receive command was issued but no interrupt occurred.  |

### 3.4.4.9 AUDIO TEST (A)

This test requires the operator to decide subjectively if the test passes or fails.

#### PSG SOUND

A sound is output on each of the three sound generator channels. The 5/8 sound is a sweep from low to high frequency. Verify that the sound can be heard throughout the range with no drop in audio level.

#### DMA SOUND

d.

Connect an oscilloscope at the stereo output jacks. Set the oscilloscope to 1 ms/division and 5 volts/division. There are four parts to this test. After observing the signals in each part of the test, proceed to the next part of the test by pressing the space bar. In each case the output signal amplitude should go from 0 volts to maximum amplitude in steps. The four parts of this test are as follows:

- a. Mono 1 kHz. Both channels will output the same signal which should approximate a sine wave of 5-6 volts in amplitude.

- b. Stereo 1 kHz/500 kHz. Verify that the right and left channels have the correct frequency. As one channel increases in amplitude, the other channel decreases. Maximum amplitude is 5-6 volts.

- c. Treble. A 12.5 kHz signal is output on both channels. Maximum amplitude is about 6 volts.

- Bass. a 50 kHz is output on both channels. Maximum amplitude is about 6 volts.

#### 3.4.4.10 TIMING TESTS (T)

These tests are run at power-up as well as being selectable from the menu. The MFP timers, the GSTMCU timing for VSYNC and HSYNC, and video display counters are tested. The video display test redirects display memory throughout RAM and verifies that the correct addresses are generated. Odd patterns may flash on screen as this test is run. There are two tests which check the bus timing for the Floppy Disk Controller and PSG chips. An error message is printed to the screen, then the test is run. If the test passes, the message is erased. If not, a Bus Error will occur and the message will remain. If a terminal is connected to the RS232 port, the message will not be erased, but "Pass" will be printed.

#### TIMING TEST ERROR CODES

| ТО | MFP timer error. One or more of the four timers in the MFP (U306) did not generate an interrupt on counting down .                                                                                 |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|